#### **TOPICAL REVIEW**

# Nanoscale electronic devices based on transition metal dichalcogenides

To cite this article: Wenjuan Zhu et al 2019 2D Mater. 6 032004

View the <u>article online</u> for updates and enhancements.

# IOP ebooks™

Bringing you innovative digital publishing with leading voices to create your essential collection of books in STEM research

Start exploring the collection - download the first chapter of every title for free.

# **2D** Materials

8 February 2019

25 March 2019

ACCEPTED FOR PUBLICATION 2 May 2019

PUBLISHED 3 June 2019

#### **TOPICAL REVIEW**

# Nanoscale electronic devices based on transition metal dichalcogenides

Wenjuan Zhu<sup>1</sup>, Tony Low<sup>2</sup>, Han Wang<sup>3</sup>, Peide Ye<sup>4</sup> and Xiangfeng Duan<sup>5</sup>

- Department of Electrical and Computer Engineering, University of Illinois at Urbana-Champaign, Urbana, IL, United States of America

- Department of Electrical and Computer Engineering, University of Minnesota, Minneapolis, MN, United States of America

- Department of Electrical and Computer Engineering-Electrophysics, University of Southern California, Los Angeles, CA, United States

- School of Electrical and Computer Engineering, Purdue University, West Lafayette, IN, United States of America

- <sup>5</sup> Department of Chemistry and Biochemistry, University of California, Los Angeles, CA, United States of America

E-mail: wjzhu@illinois.edu (Wenjuan Zhu)

Keywords: electronic devices, Esaki diodes, resonant tunneling diode, logic transistor, bipolar transistor, transition metal dichalcogenides, memory

#### Abstract

Two-dimensional (2D) transition metal dichalcogenides (TMDs) have very versatile chemical, electrical and optical properties. In particular, they exhibit rich and highly tunable electronic properties, with a bandgap that spans from semi-metallic up to 2 eV depending on the crystal phase, material composition, number of layers and even external stimulus. This paper provides an overview of the electronic devices and circuits based on 2D TMDs, such as Esaki diodes, resonant tunneling diodes (RTDs), logic and RF transistors, tunneling field-effect transistors (TFETs), static random access memories (SRAMs), dynamic RAM (DRAMs), flash memory, ferroelectric memories, resistitive memories and phase-change memories. We address the basic device principles, the advantages and limitations of these 2D electronic devices, and our perspectives on future developments.

# 1. Introduction

TMDs have a general formula of MX<sub>2</sub>, where M is a transition metal atom (such as Ti, Zr, Hf, V, Nb, Ta, Re, etc) and X is a chalcogen atom (such as S, Se, Te). There are over 30 different TMDs with diverse properties, ranging from semiconductors (MoS<sub>2</sub>, WSe<sub>2</sub>) to semimetals (1T' phase WTe<sub>2</sub> and TiSe<sub>2</sub>), metals (VSe<sub>2</sub>,  $NbS_2$ ), and superconductors ( $PbTe_2$ ,  $NbSe_2$ ) [1–16]. Monolayer TMDs have four polymorphs: 1H phase (space group  $P\overline{6}m2$ ), 1T phase (space group  $P\overline{3}m2$ ), 1T' phase (space group  $P2_1/m$ ), and  $1T_d$  phase (space group P1m1) [17-23]. When the TMDs are stacked together, they can form three types of structural polytypes: 2H (hexagonal symmetry, two layers per repeat unit, trigonal prismatic coordination), 3R (rhombohedral symmetry, three layers per repeat unit, trigonal prismatic coordination) and 1T (tetragonal symmetry, one layer per repeat unit, octahedral coordination) [24]. Most of the bulk TMDs (such as WS<sub>2</sub> and MoTe<sub>2</sub>) are stable in 2H phase and exhibit semiconductor behavior, while some of the TMDs (such as WTe<sub>2</sub>) are stable in the 1T phase and exhibit metallic behavior at room temperature [25]. These

diverse crystal structures and material properties make TMDs attractive candidates for a large variety of electronic and photonic applications. In addition, unlike graphene, TMDs can be synthesized on insulating substrates in large scale, which is another important factor that drives intense research and development interest in TMDs. The common synthesis methods for TMDs include chemical vapor deposition (CVD) [26–36], physical vapour deposition (PVD) [37, 38], metal-organic CVD (MOCVD) [39, 40], metal transformation [41], chemical vapor transport (CVT) [42, 43], chemical or electrochemical exfoliation [44-46], pulsed laser deposition (PLD) [47], molecular beam epitaxy (MBE), spray pyrolysis [48], and atomic layer deposition (ALD) [49, 50]. Among these methods, CVD and MOCVD are the most widely investigated methods and wafer-scale TMDs have been demonstrated using MOCVD [39]. The band structure, synthesis, material properties, and applications of various 2D materials including graphene, transition metal dichalcogenide and black phosphorus have been reviewed in several articles [1,4, 24, 32, 50–57]. In this paper, we focus on the electronic devices based on TMD materials and provide

comprehensive overview of the operating principles, the state-of-the-art, the potential and the challenges of TMD based electronic devices.

#### 2. Electronic devices based on TMDs

#### 2.1. Two-terminal devices

Esaki diodes and RTDs are two-terminal devices with prominent negative differential resistance (NDR). An Esaki diode is based on interband tunneling, while an RTD is based on intraband tunneling.

#### 2.1.1. Esaki diodes

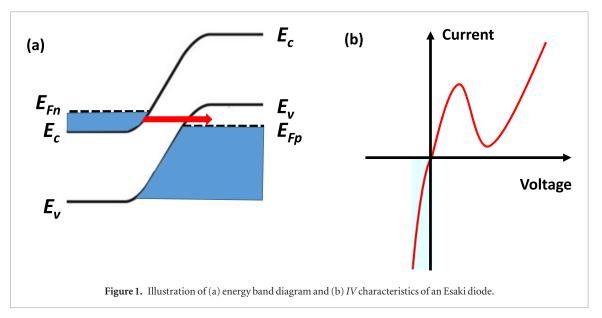

The band diagram and typical IV characteristics of the traditional Esaki diode are shown in figures 1(a) and (b) [58]. In the forward bias, electrons flow from the filled states in the conduction band in the n-type semiconductor to empty states in the valence band in the p-type semiconductor. As the forward bias is increased, the conduction band of the n-type semiconductor is eventually raised above the valence band of the p-type semiconductor, electrons can no longer tunnel into a valence-band state while conserving both total energy and transverse momentum, and the current is reduced to a minimum. Further increasing the bias will increase the current due to the thermionic emission over the energy barrier.

Various material stacks have been used in Esaki diodes, including Si, Ge, SiGe, III–V, and their heterostructures [59–65]. Peak current density up to 2.2 MA cm<sup>-2</sup> has been demonstrated in Esaki diodes based on InAs/GaSb heterojunctions [61]. Excellent average peak-to-valley current ratio (PVR) of 14 was achieved in Esaki diodes based on n-In<sub>0.5</sub>Ga<sub>0.5</sub>As/p-GaAs<sub>0.5</sub>Sb<sub>0.5</sub> [66]. Recently, 2D crystals have emerged as promising candidates for Esaki diodes. 2D materials are free of surface dangling bonds, and 2D heterostructures mediated by van der Waals (vdW) forces are free of dislocations even when there is a large mismatch in their lattice constants. The ability to stack heterostructures

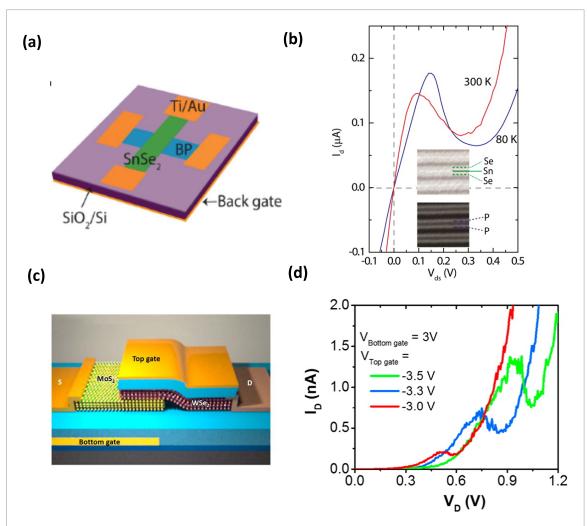

without the constraint of lattice matching opens up tremendous opportunities in the engineering of various band alignments for tunneling devices, down to the atomic level. Yan et al demonstrated Esaki diodes based on the vdW heterostructure of black phosphorus (BP) and tin diselenide (SnSe<sub>2</sub>), shown in figures 2(a) and (b) [67]. These two semiconductors form a type III or broken-gap energy band alignment. The presence of an vdW gap, which serves as a thin insulating barrier between BP and SnSe2, enables the observation of a prominent NDR region in the forward-bias region. PVR of 1.8 at 300 K and peak current density ~1.6 kA m<sup>-2</sup> were observed [67]. Esaki diode based on vertical heterostructure of MoS<sub>2</sub> and WSe<sub>2</sub> also shows NDR at low temperatures (figures 2(c) and (d)) [68]. Shim et al demonstrated an Esaki diode based on a phosphorene/rhenium disulfide (BP/ReS<sub>2</sub>) heterojunction. The PVR ratio of these devices can reach 4.2 at room temperature. Utilizing these diodes, the authors developed multi-valued logic circuits [69]. Recently, Esaki diodes based on 2D/3D heterojunctions also have been explored. Xu et al demonstrated Esaki diodes based on MoS<sub>2</sub> on degenerately-doped silicon, while Krishnamoorthy et al demonstrated Esaki diodes based on MoS<sub>2</sub> on GaN [70,71]. The PVR ratios of these 2D/3D Esaki diodes are ~1.2 [69-71]. Further material and process optimizations are still needed for the 2D TMD based Esaki diodes to be competitive with the III-V based Esaki diodes. However, the ability to freely stack the 2D layers and manipulate their orientation angle allows for greater degree of band alignment control, an attractive attribute for tunneling based devices.

#### 2.1.2. Resonant tunneling diodes (RTDs)

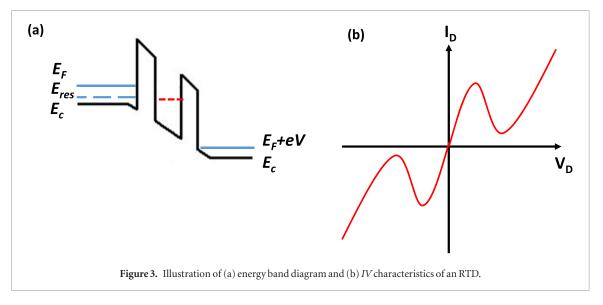

The band diagram and typical IV characteristics of a traditional RTD are illustrated in figures 3(a) and (b) [58]. The RTD consists of a double potential barrier. The quasi-Fermi levels in the left contact,  $E_{\rm F}$  and right contact,  $E_{\rm F}$ —eV, are split by the applied voltage V. The horizontal line between the barriers represents the

IOP Publishing

2D Mater. 6 (2019) 032004

W Zhu et al

**Figure 2.** Esaki diodes based on 2D TMDs. (a) and (b) Structure and current–voltage characteristics of the BP/SnSe<sub>2</sub> vdW Esaki diode [67]. (c) and (d) Three-dimensional schematic and  $I_DV_D$  of an Esaki diode based on a vertical heterostructure of MoS<sub>2</sub> and WSe<sub>2</sub> [68].

energy of the resonant state of the semiconductor in the quantum well. As bias is applied on the right contact, the resonant level is pulled down to the Fermi level of the emitter on the left. At this point, when  $E_{\rm res}=E_{\rm B}$  the

current turns on. As the bias is increased, the resonant level is pulled deeper into the Fermi sea of the emitter and the current increases with bias. Once the resonant energy falls below the conduction band of the emitter,

2D Mater. **6** (2019) 032004 W Zhu et al

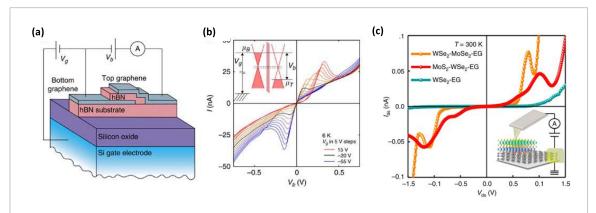

**Figure 4.** RTDs based on 2D materials. (a) and (b) Schematic diagram and measured current–voltage characteristics of a graphene-BN RTD [72]. (c) Experimental *I–V* traces for different combinations of dichalcogenide-graphene interfaces [76].

electrons can no longer tunnel while conserving both total energy and transverse momentum, and the current reaches a minimum.

Vertical stacking of 2D materials can form a double potential barrier naturally without any lattice matching restriction. It was observed experimentally that resonant tunneling can occur when the energy bands of two 2D semiconductors separated by a tunneling barrier are aligned. Britnell et al reported resonant tunneling of Dirac fermions in two graphene layers through a boron nitride barrier, shown in figures 4(a) and (b). The resulting NDR in the device characteristics persists up to room temperature and is gate-voltage tunable. Since the carriers tunnel across only a few atomic layers, these devices have the potential of ultrafast transit times [72]. Zhao et al simulated a symmetric tunneling field-effect transistor (SymFET) which consists of an n-type graphene layer and a p-type graphene layer. The authors found that a large current peak occurs when the Dirac points of the two graphene layers are aligned at a particular drain-to-source bias and the resonant current peak is controlled by chemical doping and applied gate bias [73]. NDR has also been observed in rotationally aligned double bilayer graphene heterostructures separated by hexagonal boron nitride (hBN) dielectric [74, 75]. In addition, NDR effects exist in TMD heterostructures as well. Lin et al demonstrated direct synthesis of atomically thin TMDs on graphene [76]. The conductive atomic force microscopy (CAFM) measurements on MoS2-WSe2graphene and WSe<sub>2</sub>-MoS<sub>2</sub>-graphene heterostructures show resonant tunneling and room-temperature NDR characteristics, shown in figure 4(c). The NDR and fast response time in Esaki didoes and RTDs make them promising in applications including oscillators, THz detectors, multi-value memories, and analog-todigital converters. However, a key challenge in making these vertical heterostructure based devices is the stringent requirement on matching the momentum space between layers; otherwise, transport across the layers would be phonon-mediated and would tend to degrade the performance [77].

#### 2.2. Transistors

#### 2.2.1. Logic transistors

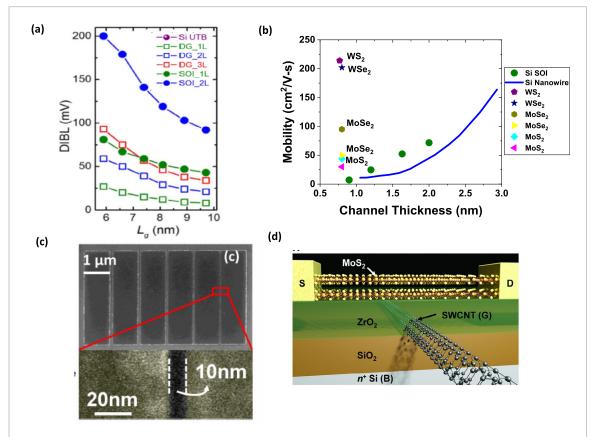

Traditional logic transistors based on silicon are facing severe challenges in device scaling. A common approach used to suppress short-channel effect involves reducing the channel thickness to enhance the gate electrostatic control on the channel. In the past, silicon-on-insulator (SOI), ultra-thin SOI (UTSOI) and extremely thin SOI (ETSOI) have been pursued [78, 79]. However, the mobility degrades and threshold voltage varies significantly as the thickness is scaled down due to surface roughness [80-83]. TMDs with atomically thin body and sizable bandgap can uniquely address these challenges [55, 84]. Simulations revealed that monolayer MoS<sub>2</sub> FETs show 52% smaller draininduced barrier lowering (DIBL) and 13% smaller subthreshold swing (SS) than 3 nm thick-body Si FETs at a channel length of 10 nm [85]. Figure 5(a) shows that monolayer MoS2 with double gate can effectively reduce DIBL as compared to silicon SOI technology [86]. In the meantime, 2D materials suffer much less mobility degradation as compared to silicon, when the channel thickness reduces to nanometer scale, shown in figure 5(b). Cao's simulation indicated that MoS<sub>2</sub> FETs can meet high performance (HP) requirement up to 6.6 nm gate length using bilayer MoS<sub>2</sub> as the channel material. The scaling of the TMD transistors was also explored experimentally [87–89]. Yang et al demonstrated scaled devices with 10 nm channel length as well as ultrathin (2.5 nm) gate dielectrics which show effective immunity to shortchannel effects, shown in figure 5(c) [90]. Desai et al demonstrated MoS<sub>2</sub> transistors with a 1 nm physical gate length using a single-walled carbon nanotube (SWCNT) as the gate electrode, illustrated in figure 5(d). These ultra-short devices show near ideal subthreshold swing of ~65 mV per decade and high On/Off current ratio of  $\sim 10^6$  [91]. These results clearly show that TMDs have high potential in extremely scaled logic devices.

Due to the atomically thin bodies and large bandgaps of TMD materials, the contact resistances in 2D Mater. **6** (2019) 032004 W Zhu *et al*

**Figure 5.** Scaling of TMD logic transistors. (a) Drain-induced barrier lowering (DIBL) with gate length scaling for 1L–3L MoS<sub>2</sub> FETs and Si ultra-thin-body (UTB) transistor. SOI and DG stand for semiconductor-on-insulator and double-gate, respectively [86]. (b) Carrier mobility as a function of channel thickness. Data for WS<sub>2</sub>, WSe<sub>2</sub>, MoSe<sub>2</sub> and MoS<sub>2</sub> are taken from [31, 39, 171–175]. Data for silicon SOI and silicon nanowire are taken from [176, 177]. (c) SEM image of the MoS<sub>2</sub> transistors with 10, 20, 40, 60, and 80 nm nominal channel length after the deposition of 40 nm Ni. Magnified part shows the 10 nm nominal channel length [90]. (d) Schematic of 1D2D-FET with a MoS<sub>2</sub> channel and SWCNT gate [91].

TMD transistors are usually much higher than those in transistors based on graphene and black phosphorus [92]. Reducing contact resistance in TMD transistors is one of the key issues that needs to be addressed before 2D TMD based electronic and photonic devices can be competitive with the current state-of-the-art electronic devices. Several approaches have been investigated to reduce contact resistance [93], including using low work-function metals for n-channel FETs (high work function for p-channel FETs) [94, 95], increasing doping in the source/drain region [96–98], converting semiconducting 2H phase to metallic 1T phase at the contact region [99], or using graphene as contact to resolve the Fermi-level pinning issues and tune the work function electrically [100–103].

The performance of the TMD transistors is also influenced by the defects in the TMD layers, the charge impurities and the topography of the gate dielectrics and the substrates [104–107]. Zhu *et al* quantified the density of the gap states in CVD MoS<sub>2</sub> on SiO<sub>2</sub> substrate and found that the trapped charges can degrade subthreshold slope, and also lead to a large underestimation of the true band mobility [88]. Cui *et al* showed that encapsulating MoS<sub>2</sub> layers with hexagonal boron nitride, in conjunction with the utilization of edge contact, can significantly reduce the extrinsic scatter-

ing and demonstrated Hall mobility of  $34\,000\,\text{cm}^2\,\text{V}^{-1}$  s<sup>-1</sup> for six-layer MoS<sub>2</sub> at low temperature (~3 K) [103].

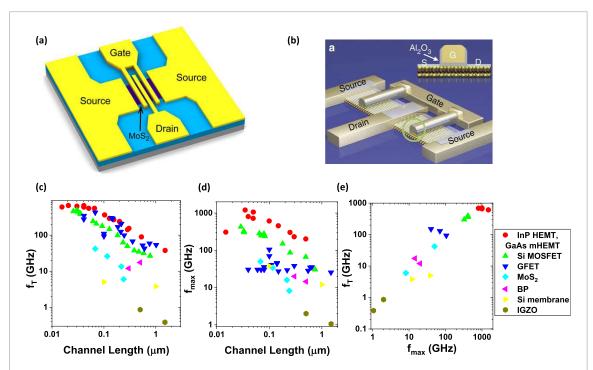

#### 2.2.2. RF transistors

Traditional RF devices were typically based on silicon, SiGe and III-V materials. The maximum frequency of oscillation,  $f_{max}$ , based on III–V materials has exceeded 1 THz [108]. To further increase the operating frequency and bandwidth, higher mobility and saturation velocity material and further optimized device structures/processes with less geometric and parasitic capcitance are needed. Graphene was intensely investigated as a potential candidate for RF devices, due to its extremly high carrier mobility. The cut-off frequency,  $f_T$ , of graphene RF devices was shown to be comparable to that of the best available III–V RF devices [109–113]. However, since graphene does not have a bandgap, it is very difficult to achieve current saturation, which will limit the  $f_{max}$  and power gain of the RF devices. TMDs with sizable bandgap can potentially address this issue. Krasnozhon et al demonstrated top-gated MoS<sub>2</sub> RF transistors with  $f_T$  reaching 6 GHz and  $f_{max}$  of 8.2 GHz on silicon substrate, illustrated in figure 6(a) [114]. Cheng et al demonstrated a high-performance MoS<sub>2</sub> RF device on flexible substrate with an intrinsic cut-off frequency  $f_T$

**Figure 6.** RF transistors based on TMDs. (a) An illustration of a MoS<sub>2</sub> RF device with metal gate. (b) A schematic illustration of a dual-channel self-aligned MoS<sub>2</sub> FET with transferred gate stacks, and the inset shows the schematic cross-section of the self-aligned device. (c) Cut-off frequency  $f_T$  and (d) maximum oscillation frequency  $f_{max}$  as a function of gate length of MoS<sub>2</sub> RF transistors, together with the representative results for RF devices based on graphene, black phosphorus (BP), InP, GaAs, Si, IGZO and silicon nanomembranes. (e)  $f_T$  versus  $f_{max}$  of MoS<sub>2</sub> RF transistors, together with the best results reported for RF devices based on graphene, BP, InP, GaAs, Si, IGZO and silicon nanomembranes. For (c)–(e), data for MoS<sub>2</sub> RF transistor are taken from [114, 115]. Data for black phosphorus are taken from [178, 179]. Data for graphene is taken from [111, 180–182]. Data for SI MOSFET, InP HEMT and GaAs HEMTs are taken from [182, 183]. Data for silicon nanomebranes are taken from [184, 185]. Data for IGZO are taken from [186, 187].

up to 42 GHz and a maximum oscillation frequency  $f_{max}$  up to 50 GHz, and an intrinsic gain over 30, shown in figure 6(b) [115]. Figures 5(c) and (d) show  $f_T$  and  $f_{max}$  of TMD RF devices, together with the best RF devices based on graphene, black phosphorus, silicon, III-V materials, silicon nanomembranes and indium gallium zinc oxide (IGZO). For flexible electronics, the RF devices based on TMDs are very promising, as the  $f_T$  and  $f_{max}$  of the TMD RF devices are higher than or comparable to that of RF devices based on other flexible electronic materials such as silicon membrane and IGZO. For electronics on rigid substrates, however, RF devices based on III-V materials and silicon are more promising, since TMDs have limited mobilities and high contact resistances. The issue of limited mobilities should become less important as device channel length approaches that of the scattering mean free path, and entering the ballistic transport limit. Achieving low Ohmic contact resistance presents a more pressing issue in this regard.

#### 2.2.3. Tunneling field-effect transistors (TFETs)

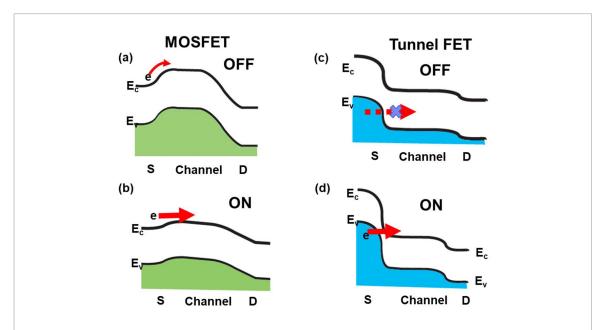

Power consumption is one of the main challenges for future electronics. Reducing the subthreshold swing is key to lowering the supply voltage and power consumption. In a conventional MOSFET, the minimum subthreshold swing (SS) is 60 mV/decade at room temperature, determined by the thermal

energy of the carriers. This places a fundamental limit on the supply voltage. TFET can overcome this limit by using band-to-band tunneling, rather than thermal injection, to inject charge carriers into the device channel [116–118]. In TFETs, the carriers in the source are energetically forbidden to tunnel to the channel in the OFF state, due to the lack of available states in the channel, illustrated in figure 7(c). This effectively cuts off the current induced by the carriers in the highenergy tail of the Femi-Dirac distribution. When the device is turned on, i.e. the conduction band of the channel is below the valence band edge of the source region, the electrons can now tunnel from the source to the channel, as illustrated in figure 7(d). This ON/OFF switch is controlled by the availability of the energy states in the channel, instead of the carrier energy distribution, resulting in a much steeper subthreshold swing in TFET as compared to MOSFET.

Researchers have explored various TFET devices using group IV semiconductors [119, 120], III–V semiconductors [121], and carbon based materials [122]. InAs/silicon heterostructure TFETs show subthreshold swing as low as 20 mV/decade; however, the on-current is only ~6 nA  $\mu$ m<sup>-1</sup> [123, 124]. Type II arsenide/antimonide compound semiconductor with highly staggered GaAs<sub>0.35</sub>Sb<sub>0.65</sub>/In<sub>0.7</sub>Ga<sub>0.3</sub>As heterojunction demonstrated very high on-current (190  $\mu$ A  $\mu$ m<sup>-1</sup> at  $V_{DS} = 0.75$  V); however, the subthreshold

**IOP** Publishing 2D Mater. **6** (2019) 032004 W Zhu et al

**Figure 7.** Energy diagram of MOSFET and TFETs. Figures (a) and (b) are the energy diagrams of a MOSFET at OFF and ON states. Figures (c) and (d) are the energy diagrams of a TFET at OFF and ON states.

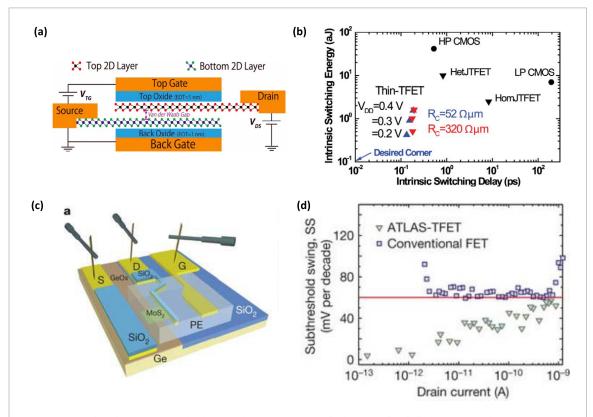

Figure 8. TFETs based on 2D TMDs. (a) Schematic device cross section of a thin-TFET [130]. (b) Intrinsic switching energy and delay for high performance (HP) CMOS, low power (LP) CMOS, heterojunction TFET (HetJTFET), homojunction TFET (HomJTFET), and thin-TFETs with  $V_{\rm DD}=0.2,0.3,0.4$  V, and  $R_{\rm C}=52,320~\Omega\mu m$  [130]. (c) Schematic diagram showing the probing configuration for measurement of the characteristics of the ATLAS-TFET [133]. (d) SS as a function of drain current for an ATLAS-TFET (green triangles) as well as a conventional MOSFET (blue squares) at  $V_{\rm DS}=0.5$  V. The red line demarcates the fundamental lower limit of SS of conventional FETs [133].

swing in this device is very high ( $\sim$ 750 mV/decade) [125]. However, one should note that the presence of hysteresis can often mask the true SS of the device.

The key challenges in TFETs are the formation of atomically sharp transition between n-i-p regions and reduction of the interface traps. In recent years, 2D materials emerged that can be stacked on top of each other to form atomically sharp pn junctions. In addition, the 2D materials are free of surface dangling bonds, which potentially can reduce the interface states. Simulation of the TFETs based on 2D TMDs, their heterostructures and superlattices shows very

IOP Publishing

2D Mater. 6 (2019) 032004

W Zhu et al

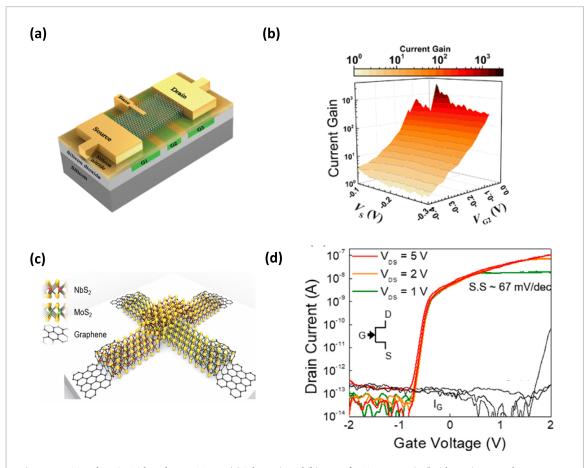

Figure 9. BJTs and MESFETs based on 2D TMDs. (a) Schematic and (b) map of BJT current gain  $\beta$  with varying  $V_S$  and  $V_{G2}$  determined at  $V_D = 0.2 \text{ V} [134]$ . (c) A 3D schematic view of atomic layer NbS<sub>2</sub>/MoS<sub>2</sub> MESFET [139]. (d)  $I_D$ – $V_{GS}$  transfer and  $I_G$ – $V_{GS}$  gate leakage curves of the MESFET, as measured with  $V_{DS}$  increase [139].

promising results [126]. For example, Ghosh's simulation of the lateral TFETs based on five MX<sub>2</sub> materials (MoS<sub>2</sub>, MoSe<sub>2</sub>, MoTe<sub>2</sub>, WSe<sub>2</sub>, WSe<sub>2</sub>) shows steep SS (4 mV/decade) and high on-current (150  $\mu$ A  $\mu$ m<sup>-1</sup> at  $V_d = 0.1$  V) [127]. Planar TFET based on narrow bandgap material Bi<sub>2</sub>Se<sub>3</sub> (0.252 eV) can operate under ultralow supply voltage of 0.2 V, with an ON/OFF current ratio of  $10^4$  [128].

TFETs made of a vertical heterojunction of singlelayer MoTe<sub>2</sub> and SnS<sub>2</sub> show on-currents >75  $\mu$ A  $\mu$ m<sup>-1</sup> and the inverse subthreshold slope reaches 25 mV/ decade at 0 V [129], while TFETs based on WSe2/SnSe2 heterostructure can reach a steep subthreshold swing (SS) of  $\sim$ 14 mV/decade and a high on-current of  $\sim$ 300  $\mu$ A  $\mu$ m<sup>-1</sup> [130]. Li's simulation shows that 2D TFETs may outperform CMOS and III-V TFETs in terms of both switching speed and energy consumption at low supply voltages (figures 8(a) and (b)) [130]. Lu et al simulated TFETs based on MoS<sub>2</sub>/WSe<sub>2</sub> superlattices and found that the on-current of the TFETs based on the superlattices is more than 4 orders of magnitude greater than that in TFETs based on MoS2 or MoSe2 homojunction [131]. However, there are very few experimental results of TFETs showing subthreshold swing below 60 mV/decade. The key challenge of the 2D TFETs is the interface states in the real devices, which can severely degrade subthreshold swing. TFETs based on WSe<sub>2</sub>/SnSe<sub>2</sub> heterostructures with

clean interfaces yield a subthreshold swing of 100 mV/ decade for more than two decades of drain current at room temperature [132]. Recently, Sarkar et al demonstrated vertical TFETs based on highly doped germanium and atomically thin MoS<sub>2</sub> with solid polymer electrolyte as gate dielectric, which exhibit minimum subthreshold swing of 3.9 mV/decade and an average subthreshold swing of 31.1 mV/decade for four decades of drain current at room temperature, shown in figures 8(c)-(e) [133]. These TFETs will have broad applications from mobile devices to medical implantable devices and data centers. The availability of a large library of 2D materials would offer ideal materials alignment needed for TFET applications. Low et al recently surveyed a wide range of 2D semiconductor band alignments and identified combinations with momentum matched type III heterostructures [77]. Type III band alignment is most favorable in terms of yielding a larger ON state current.

#### 2.2.4. Bipolar transistor

A traditional bipolar transistor (BJT) typically consists of a pnp or npn junction. Unlike MOSFET, where only one type (unipolar) of carrier dominates the current transport in a given device, in BJT, both types (bipolar) of carrier are involved. BJT is commonly used for current amplification. Traditionally the npn and pnp junctions were fabricated by local doping of the

silicon wafers. Recently, Agnihotri et al demonstrated a BJT device based on WSe<sub>2</sub> by using buried gates to electrostatically create doped regions with back-toback pn junctions. These WSe<sub>2</sub> bipolar transistors show a current gain of 1000 and photocurrent gain of 40, shown in figures 9(a) and (b) [134]. The key advantage of this new type of the bipolar transistor is the re-configurability, where an npn BJT can be dynamically reconfigured into a pnp BJT using electrical signal, a feature non-existent in traditional semiconductor based BJT. In addition to these homojunction bipolar transistors, heterojunction bipolar transistors (HBT) based on TMDs were also explored. HBTs based on 2D TMDs can address several challenges in traditional HBTs based on bulk materials, such as dopant diffusion, lattice match restriction and dislocation propagation. Lin et al demonstrated lateral HBT based on p-WSe<sub>2</sub>/n-MoS<sub>2</sub> junctions with current gain of around 3 [135]. Lee et al fabricated vertical HBTs based on n-MoS<sub>2</sub>/p-WSe<sub>2</sub>/n-MoS<sub>2</sub> stacks, which show very high current gain (~150) [136]. These prototype bipolar devices open a new application for 2D heterostructures in analog and high-frequency electronics.

#### 2.2.5. Junction field-effect transistor (JFET)

JFET uses the depletion in a pn junction to control the current in the channel. The depletion-layer width of the pn junction can be varied by modulating a reversebias voltage applied to the junction. Traditional JFETs based on silicon were fabricated by forming the local doping. In 2D materials, these pn junctions can be formed by stacking n- and p-type TMDs or by combining TMDs with other materials, which have complementary doping types. Kim et al demonstrated an n-channel depletion-mode  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> junction JFET through van der Waals bonding with an exfoliated p-WSe<sub>2</sub> flake [137]. These heterojunction JFETs exhibited excellent transfer and output characteristics with a high ON/OFF ratio ( $\sim 10^8$ ) and low subthreshold swing (133 mV/decade). VdW JFETs based on n-MoS<sub>2</sub> and p-MoTe<sub>2</sub> were also demonstrated with ON/OFF current ratio up to  $10^4$  [138].

# 2.2.6. Metal semiconductor field-effect transistor (MESFET)

In a MESFET, a metal-semiconductor Schottky barrier instead of a pn junction is used for the gate electrode. As compared to JFETs, the potential advantages of MESFETs are low-temperature process, low gate resistance and good heat dissipation. Shin *et al* demonstrated vdW MESFETs based on metallic NbS<sub>2</sub> and semiconducting n-MoS<sub>2</sub>, illustrated in figure 9(c). The Schottky-effect MESFET displays little gate hysteresis and an ideal subthreshold swing of 60–80 mV/decade due to low-density traps at the vdW interface, shown in figure 9(d) [139].

#### 2.3. Memory devices

Semiconductor memory is a digital electronic data storage device. Random access memory (RAM) is semiconductor memory, which allows data items to be read or written in almost the same amount of time irrespective of the physical location of data inside the memory. There are two types of RAM: volatile memory, which loses its stored data when the power to the memory chip is turned off, and nonvolatile memory, which preserves the data stored in it during periods when the power to the chip is turned off. Major types of volatile memory are dynamic RAM (DRAM) and static RAM (SRAM). The major types of nonvolatile memory are flash memory, resistive RAM (RRAM), ferroelectric RAM (FRAM), phasechange RAM (PCRAM), and magnetoresistive RAM (MRAM). Volatile memories can be faster than nonvolatile memories, while nonvolatile memories can consume less power and save the data while the power is off. Volatile memories are typically used as the main memory in the computers, while nonvolatile memories, such as flash memories, are typically used as solid-state hard drives, and in portable devices such as personal digital assistants (PDAs), USB flash drives, and removable memory cards used in digital cameras and cell phones.

#### 2.3.1. SRAM

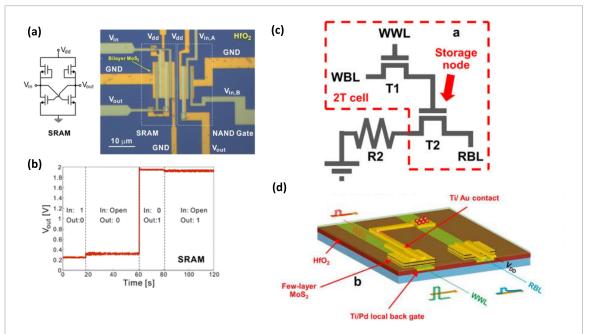

SRAM is a type of semiconductor memory that uses bistable latching circuitry (flip-flop) to store each bit. A typical SRAM cell is made up of six MOSFETs (2 pFETs and 4 nFETs). TMDs with sizable bandgap and atomically thin body, which provide excellent immunity to short-channel effects, are very attractive for future extremely-dense low-voltage SRAM arrays. Han et al demonstrated functional SRAM based on bilayer MoS<sub>2</sub> using direct-coupled FET logic technology, shown in figures 10(a) and (b) [140]. In order to form devices with different threshold voltages, the authors used metals with different work functions as the gate electrodes to form depletion-mode and enhancement-mode transistors. TCAD simulation reveals that monolayer TMDs with excellent device electrostatics and superior stability are promising for low-power SRAM applications, while the bilayer TMDs, with higher carrier mobility, are more suitable for high-performance SRAM applications [141].

#### 2.3.2. DRAM

DRAM is a type of random access memory that stores each bit of data in a separate capacitor. The capacitor can either be charged or discharged. These two states are taken to represent the two values of a bit, conventionally called '0' and '1'. A typical DRAM cell consists of one transistor and one capacitor (1T1C). In this type of DRAM cell, the read is destructive and a write-back operation is needed. Recently Kshirsagar

Figure 10. SRAM and DRAM based on 2D TMDs. (a) Optical micrograph, schematics of the electronic circuits, and (b) output voltage of a flip-flop memory cell (SRAM) based on  $MoS_2$  [140]. (c) Circuit schematic and (d) illustration of 2T DRAM memory cell based on  $MoS_2$  [142].

et al demonstrated a DRAM cell based on two  $MoS_2$  transistors, shown in figures 10(c) and (d) [142]. In this DRAM cell, the read is non-destructive. In addition, since  $MoS_2$  has wide bandgap (1.8 eV in monolayer) and high effective masses, which lead to extremely low OFF-state leakage currents, this new type of DRAM is promising for low-power applications [142].

# 2.3.3. Flash memory

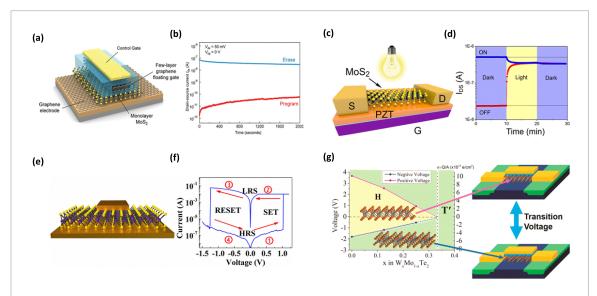

Flash memory stores information in an array of memory cells made from floating-gate transistors. In the traditional flash memory, the floating gate is typically made of a polycrystalline silicon conductive layer. Bertolazzi et al demonstrated a floating gate memory device using graphene as the floating gate and MoS<sub>2</sub> as the channel, as shown in figures 11(a) and (b). Due to its 2D nature, monolayer MoS<sub>2</sub> is highly sensitive to the presence of charges in the charge trapping layer, which leads to a ratio of channel resistance (10<sup>4</sup>) between memory program and erase states [143]. Cao et al had shown that employing multilayer graphene as floating gate can effectively reduce cell-to-cell interference (CTCI) and threshold voltage variation due to reduced floating gate thickness. In addition, due to the band offset between graphene and TMD layer, the stored electrons in the graphene floating gate are unlikely to leak out, which can help to prolong the retention of the memory cell [144]. The reverse device structure, where graphene serves as the channel and MoS2 is used as the charge trapping layer, was also demonstrated [145]. Large memory window and stable retention were observed in these devices [145].

#### 2.3.4. FRAM

FRAM utilizes ferroelectric polarization switching for data storage. In a FRAM cell, the dipoles tend to align themselves with the field direction when an external electric field is applied to the dielectric structure. The dipoles retain the polarization state after the electric field is removed. Therefore, FRAM is ideally nonvolatile. Typically, the memory cell in FRAM consists of 1 transistor (1T), or 1 transistor and 1 capacitor (1T1C). In the 1T1C structure, the read operation is destructive and a 'write-back' operation is needed, which can severely degrade the endurance of the memory cell. In the 1T structure, however, the read operation is nondestructive, which provides advantages including high endurance and low energy consumption. Lipatov et al fabricated ferroelectric memory based on MoS2 on a lead zirconium titanate (Pb(Zr,Ti)O<sub>3</sub>,PZT) substrate that was used as a gate dielectric, shown in figures 11(c)and (d). The MoS<sub>2</sub>/PZT ferroelectric transistors exhibit a large hysteresis and high ON/OFF ratios. Interestingly, the authors found that this type of FRAM can be written and erased both electrically and optically [146]. Ferroelectric memory devices based on monolayer MoS<sub>2</sub> and aluminium (Al)doped hafnium oxide (HfO2) as the ferroelectric gate dielectric were also demonstrated [147]. These memory transistors show sizable memory window and clear wake-up effect [147]. Recently, Si et al demonstrated FRAM based on MoS2 and 2D ferroelectric material CuInP<sub>2</sub>S<sub>6</sub>, which opens up a new route toward ferroelectric memories based on vdW heterostructures [148].

Figure 11. Nonvolatile memories based on 2D TMDs. (a) Three-dimensional schematic view of the memory device based on single-layer  $MoS_2$  [143]. (b) Temporal evolution of drain-source currents ( $I_{ds}$ ) in the erase (ON) and program (OFF) states. The drain-source bias voltage is 50 mV and the duration of the control-gate voltage pulse is 3 s [143]. (c) Schematic of and (d) effect of visible light illumination on the data retention characteristics of a  $MoS_2/PZT$  FeFET [146]. (e) Schematic and (f) typical I-V curves of monolayer TMD atomristors [150]. (g) Positive (pink) and negative (blue) voltage required to switch the relative stability of H-MoTe<sub>2</sub> and T'-MoTe<sub>2</sub> [157].

#### 2.3.5. RRAM

RRAM is based on an array of memristors, where the high-resistance and low-resistance states are used to store data. Traditional memristors were mainly based on metal oxide, such as titanium oxide or tantalum oxide. Wang et al demonstrated a memristor based on a van der Waals heterostructure composed of graphene/MoS<sub>2-x</sub>O<sub>x</sub>/graphene. These memristors exhibit excellent switching performance with an endurance of up to 10<sup>7</sup> and a high operating temperature of up to 340 °C. The authors attribute the switching mechanism to the migration of oxygen ions in MoS<sub>2-x</sub>O<sub>x</sub> [149]. Ge et al demonstrated vertical memristors based on various TMDs including MoS<sub>2</sub>,  $WS_2$ ,  $MoSe_2$  and  $WSe_2$ , shown in figures 11(e) and (f). Stable nonvolatile resistance switching was observed in these single-layer atomic TMD sheets sandwiched between metal electrodes [150]. These memristors can be used as nonvolatile flexible memory fabrics and in brain-inspired (neuromorphic) computing.

### 2.3.6. PCRAM

PCRAMs are based on phase-change materials that exist in two or more phases with different properties [151, 152]. These phases typically correspond to different resistances which can be used to store data. There are mainly two types of PCM: metal oxides (such as  $VO_2$  and  $NbO_2$ ) which can undergo a Mott metal-to-insulator transition [153], and chalcogenide glasses (such as  $Ge_2Sb_2Te_5$ ) which can have amorphous-to-crystalline phase transition [152]. It was discovered recently that Mo- and W-dichalcogenides can exist in several 2D phases (2H and 1T or 1T' phase) [154, 155]. The energy differences between the H and T' monolayer phases, for six pure  $MX_2$  compounds (M = Mo or W, X = S, Se or Te), were calculated

using DFT [25]. MoTe<sub>2</sub> and WTe<sub>2</sub> have the smallest energy difference between H and T' phase, which makes them the best candidates for phase transitions in these 2D materials [25]. More interestingly, the energy difference between H and T' is positive for MoTe<sub>2</sub>, while it is negative for WTe<sub>2</sub>, which means that MoTe<sub>2</sub> is stable in the 2H phase, while WTe<sub>2</sub> is stable in the 1T' phase. Alloying these two materials can lower the energy barrier between these two phases and the transition temperature can be tuned continuously from 0K to  $\sim 933K$  [156]. In the past, the phase transition was mainly achieved by thermal effect (Joule heating and laser illumination). The high reset current and the heat dissipated to the surrounding materials consume a large amount of energy. It was discovered recently that 2D phase change materials such as MoTe<sub>2</sub> and Mo<sub>x</sub>W<sub>1-x</sub>Te<sub>2</sub> can achieve phase transition by electrostatic gating, shown in figure 11(g) [157-160]. Based on the theoretic calculation, the energy consumption per unit volume of the electrostatically driven phase transition in monolayer MoTe<sub>2</sub> at room temperature is 9% of the adiabatic lower limit of the thermally driven phase transition in Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> [161]. These results indicate that 2D TMDs are very promising for PCRAM applications.

# 3. Integrated circuits based on TMDs

Although TMD electronics are still in their early exploratory stage, significant progress has been made toward integrating these devices into circuits. Wang *et al* demonstrated an inverter, a NAND gate, an SRAM, and a five-stage ring oscillator using bilayer MoS<sub>2</sub> based on the direct-coupled transistor logic technology. These circuits comprise between 2 and 12 integrated transistors with bilayer MoS<sub>2</sub> channel. Both

enhancement-mode and depletion-mode transistors were fabricated by using gate metals with different work functions [140]. Tosun et al demonstrated a complementary logic inverter based on WSe2 flake [162]. High work function metal Pt was used as the contact metal for p-FET to facilitate the hole injection, while potassium was used to form degenerately doped n<sup>+</sup> contacts for n-FET to enhance electron injection. These inverters show a dc voltage gain higher than 12 [162]. Yu et al demonstrated a high-performance WSe<sub>2</sub> CMOS inverter using F<sub>4</sub>TCNQ for n-type doping. These inverters show large voltage gain (~38) and small static power (picowatts) [163]. Wachter et al moved one step further and demonstrated a 1-bit implementation of a microprocessor using a MoS<sub>2</sub> [164]. The microprocessor can execute userdefined programs stored in an external memory, perform logical operations and communicate with its periphery circuits [164]. Integrated circuits based on the combination of various 2D TMDs or combining 2D TMDs with other materials have also been demonstrated. Yu et al demonstrated a complementary inverter by vertically stacking graphene, Bi<sub>2</sub>Sr<sub>2</sub>Co<sub>2</sub>O<sub>8</sub> (p-channel), graphene, MoS<sub>2</sub> (n-channel) and a metal thin film in sequence [165]. Cho et al reported on the design of a complementary inverter, based on a MoS<sub>2</sub> n-type transistor and a WSe<sub>2</sub> p-type transistor [166]. Pezeshki et al employed a direct imprinting technique to fabricate inverters using  $\alpha$ -MoTe<sub>2</sub> for the p-channel FETs and MoS<sub>2</sub> for the n-channel FETs [167]. To avoid ambipolar behavior and produce  $\alpha$ -MoTe<sub>2</sub> FETs with clean p-channel characteristics, the authors have employed the high work function metal platinum for the source and drain contacts [167]. These inverters show voltage gains as high as 33, switching delay of 25  $\mu$ s, and static power consumption of a few nanowatts.

Beyond the planar integrated circuit, 3D integrated circuits were also explored recently. 3D integration can bring various types of circuits in close proximity in the vertical direction to achieve performance improvements with reduced power and a smaller footprint than the conventional 2D processes. A processor-in-memory (PIM) architecture has been proposed recently, wherein a logic layer is 3D stacked with a DRAM layer to reduce energy consumption related to data transfer while simultaneously increasing the performance [168, 169]. In the past, 3D integration was mainly achieved by stacking wafers/dies and interconnecting them vertically, using throughsilicon vias (TSVs). This technique has the drawbacks of high cost, long vertical distance between the wafers, and the very limited number of wafers that can be stacked. 2D materials can be stacked layer-by-layer and address this issue [51]. Yang et al demonstrated the first 1-transistor-1-resistor (1T1R) memory cell using the atomically thin MoS<sub>2</sub> FET and RRAM [170]. Yang et al demonstrated a monolithic 3D image sensor, which consists of large-area monolayer MoS<sub>2</sub> phototransistor array on top of silicon logic/memory circuits. This 3D monolithic integration of 2D TMD devices with traditional silicon circuits opens up a new route toward high-density and energy-efficient electronic and optoelectronic systems.

#### 4. Conclusion and outlook

This paper provides a comprehensive overview of electronic devices based on 2D TMDs, ranging from two-terminal devices such as Esaki didoes and RTDs, to transistors such as TFETs and RF devices, and to memories. The unique properties of 2D materials, including atomically thin body, dangling bond-free surface, and atomically sharp heterojunction interface bring new features to the traditional devices. For example, TMD heterostructures with broken-gap band alignment can enable Esaki diodes with prominent NDRs, TMD heterogeneous pn junctions enable vertical TFETs with super-steep subthreshold slope, and TMD atomically thin body provides TMD transistors with superior immunity to short-channel effects. TMDs with low energy barrier between 1H and 1T phase, such as MoTe<sub>2</sub> and Mo<sub>x</sub>W<sub>1-x</sub>Te<sub>2</sub> alloys, are very attractive for phase-change memories. The phase transition tunable by electrostatic gating can enable PCRAMs with ultralow energy consumption. In addition, 3D monolithic integration of the 2D electronic devices opens up a new route toward high-density and low-power applications. However, there are many limitations and challenges in 2D TMD electronics, such as large-scale high-quality synthesis of TMDs and contact resistance issues. Much research and development effort is still needed before these materials and devices are ready for mainstream applications. If these efforts are successful, 2D electron devices can potentially have broad applications from data centers to mobile devices, THz detectors, and wearable electronics.

## Acknowledgments

WZ would like to acknowledge support from the National Science Foundation (NSF) under Grants ECCS 16-11279 and ECCS 16-53241 CAR and from the Office of Naval Research (ONR) under grant NAVY N00014-17-1-2973. XD acknowledges the support of the Office of Naval Research through grant number N00014-15-1-2368. TL acknowledged support from NSF ECCS-1542202, and the Minnesota MRSEC under Award NSF DMR-1420013. HW acknowledges the support from Army Research Office (Grant no. W911NF-18-1-0268) and National Science Foundation (Grant no. EFMA-1542815).

# **ORCID** iDs

Wenjuan Zhu https://orcid.org/0000-0003-2824-1386

#### References

- Chhowalla M, Shin H S, Eda G, Li L-J, Loh K P and Zhang H 2013 The chemistry of two-dimensional layered transition metal dichalcogenide nanosheets *Nat. Chem.* 5 263

- [2] Fatemi V, Wu S F, Cao Y, Bretheau L, Gibson Q D, Watanabe K, Taniguchi T, Cava R J and Jarillo-Herrero P 2018 Electrically tunable low-density superconductivity in a monolayer topological insulator *Science* 362 926

- [3] Sajadi E, Palomaki T, Fei Z Y, Zhao W J, Bement P, Olsen C, Luescher S, Xu X D, Folk J A and Cobden D H 2018 Gateinduced superconductivity in a monolayer topological insulator Science 362 922

- [4] Novoselov K S, Mishchenko A, Carvalho A and Neto A H C 2016 2D materials and van der Waals heterostructures *Science* 353 aac9439

- [5] Sie E J et al 2019 An ultrafast symmetry switch in a Weyl semimetal *Nature* 565 61

- [6] Ma Q et al 2019 Observation of the nonlinear Hall effect under time-reversal-symmetric conditions Nature 565 337

- [7] Sipos B, Kusmartseva A F, Akrap A, Berger H, Forro L and Tutis E 2008 From Mott state to superconductivity in 1T-TaS(2) Nat. Mater. 7 960–5

- [8] Yu Y J et al 2015 Gate-tunable phase transitions in thin flakes of 1T-TaS<sub>2</sub> Nat. Nanotechnol. 10 270–6

- [9] Xi X X, Zhao L, Wang Z F, Berger H, Forro L, Shan J and Mak K F 2015 Strongly enhanced charge-density-wave order in monolayer NbSe<sub>2</sub> Nat. Nanotechnol. 10 765

- [10] Joe Y I et al 2014 Emergence of charge density wave domain walls above the superconducting dome in 1T-TiSe<sub>2</sub> Nat. Phys. 10 421–5

- [11] Ugeda M M et al 2016 Characterization of collective ground states in single-layer NbSe<sub>2</sub> Nat. Phys. 12 92-U126

- [12] Xi X X, Wang Z F, Zhao W W, Park J H, Law K T, Berger H, Forro L, Shan J and Mak K F 2016 Ising pairing in superconducting NbSe2 atomic layers Nat. Phys. 12 139

- [13] Das P K *et al* 2016 Layer-dependent quantum cooperation of electron and hole states in the anomalous semimetal WTe<sub>2</sub> *Nat. Commun.* 7 11355

- [14] Ma L G et al 2016 A metallic mosaic phase and the origin of Mott-insulating state in 1T-TaS<sub>2</sub> Nat. Commun. 7 10956

- [15] Navarro-Moratalla E et al 2016 Enhanced superconductivity in atomically thin TaS $_2$  Nat. Commun. 7 11043

- [16] Yan M Z et al 2017 Lorentz-violating type-II Dirac fermions in transition metal dichalcogenide PtTe<sub>2</sub> Nat. Commun. 8 257

- [17] You J-S, Fang S, Xu S-Y, Kaxiras E and Low T 2018 Berry curvature dipole current in the transition metal dichalcogenides family *Phys. Rev.* B **98** 121109

- [18] Oliver S M et al 2017 The structural phases and vibrational properties of  $Mo_{1-x}W_xTe_2$  alloys 2d Mater. 4 045008

- [19] Yang H, Kim S W, Chhowalla M and Lee Y H 2017 Structural and quantum-state phase transitions in van der Waals layered materials (vol 13 p 931) Nat. Phys. 13 1232

- [20] Ouyang B, Lan G Q, Guo Y S, Mi Z T and Song J 2015 Phase engineering of monolayer transition-metal dichalcogenide through coupled electron doping and lattice deformation Appl. Phys. Lett. 107 21

- [21] Lin X et al 2017 Intrinsically patterned two-dimensional materials for selective adsorption of molecules and nanoclusters Nat. Mater. 16717

- [22] Liu L N  $et\,al\,2018$  Phase-selective synthesis of 1T'MoS $_2$  monolayers and heterophase bilayers  $Nat.\,Mater.\,17\,1108$

- [23] Yabuki N, Moriya R, Arai M, Sata Y, Morikawa S, Masubuchi S and Machida T 2016 Supercurrent in van der Waals Josephson junction Nat. Commun. 7 10616

- [24] Wang Q H, Kalantar-Zadeh K, Kis A, Coleman J N and Strano M S 2012 Electronics and optoelectronics of two-dimensional transition metal dichalcogenides *Nat. Nanotechnol*, 7 699

- [25] Duerloo K A N, Li Y and Reed E J 2014 Structural phase transitions in two-dimensional Mo- and W-dichalcogenide monolayers Nat. Commun. 5 4214

- [26] Lee Y H et al 2013 Synthesis and transfer of single-layer transition metal disulfides on diverse surfaces Nano Lett. 13 1852–7

- [27] Wu S F, Huang C M, Aivazian G, Ross J S, Cobden D H and Xu X D 2013 Vapor–solid growth of high optical quality MoS<sub>2</sub> monolayers with near-unity valley polarization Acs Nano 7 2768–72

- [28] Chen L, Liu B L, Abbas A N, Ma Y Q, Fang X, Liu Y H and Zhou C W 2014 Screw-dislocation-driven growth of twodimensional few-layer and pyramid-like WSe<sub>2</sub> by sulfurassisted chemical vapor deposition Acs Nano 8 11543–51

- [29] Najmaei S, Liu Z, Zhou W, Zou X L, Shi G, Lei S D, Yakobson B I, Idrobo J C, Ajayan P M and Lou J 2013 Vapour phase growth and grain boundary structure of molybdenum disulphide atomic layers Nat. Mater. 12 754–9

- [30] van der Zande A M, Huang P Y, Chenet D A, Berkelbach T C, You Y M, Lee G H, Heinz T F, Reichman D R, Muller D A and Hone J C 2013 Grains and grain boundaries in highly crystalline monolayer molybdenum disulphide Nat. Mater. 12 554–61

- [31] Zhou H L et al 2015 Large area growth and electrical properties of p-type WSe<sub>2</sub> atomic layers Nano Lett. 15 709–13

- [32] Chen P, Zhang Z, Duan X and Duan X 2018 Chemical synthesis of two-dimensional atomic crystals, heterostructures and superlattices *Chem. Soc. Rev.* 47 3129–51

- [33] Shaw J C, Zhou H L, Chen Y, Weiss N O, Liu Y, Huang Y and Duan X F 2014 Chemical vapor deposition growth of monolayer MoSe<sub>2</sub> nanosheets *Nano Res.* 7 511–7

- [34] Sahoo P K, Memaran S, Xin Y, Balicas L and Gutierrez H R 2018 One-pot growth of two-dimensional lateral heterostructures via sequential edge-epitaxy *Nature* 553 63

- [35] Lu A Y et al 2017 Janus monolayers of transition metal dichalcogenides Nat. Nanotechnol. 12 744

- [36] Han G H et al 2015 Seeded growth of highly crystalline molybdenum disulphide monolayers at controlled locations Nat. Commun. 66128

- [37] Kaindl R et al 2017 Growth structure and stability of sputterdeposited MoS(2) thin films Beil. J. Nanotechnol. 8 1115–26

- [38] Huang C, Wu S, Sanchez A M, Peters J J P, Beanland R, Ross J S, Rivera P, Yao W, Cobden D H and Xu X 2014 Lateral heterojunctions within monolayer MoSe<sub>2</sub>–WSe<sub>2</sub> semiconductors Nat. Mater. 13 1096

- [39] Kang K, Xie S E, Huang L J, Han Y M, Huang P Y, Mak K F, Kim C J, Muller D and Park J 2015 High-mobility three-atomthick semiconducting films with wafer-scale homogeneity Nature 520 656–60

- [40] Kang K, Lee K H, Han Y M, Gao H, Xie S E, Muller D A and Park J 2017 Layer-by-layer assembly of two-dimensional materials into wafer-scale heterostructures *Nature* **550** 229–33

- [41] Zhan Y, Liu Z, Najmaei S, Ajayan P M and Lou J 2012 Largearea vapor-phase growth and characterization of MoS<sub>2</sub> atomic layers on a SiO<sub>2</sub> substrate *Small* 8 966–71

- [42] Al-Hilli A A and Evans B L 1972 The preparation and properties of transition metal dichalcogenide single crystals J. Cryst. Growth 15 93–101

- [43] Agarwal M K, Nagi Reddy K and Patel H B 1979 Growth of tungstenite single crystals by direct vapour transport method J. Cryst. Growth 46 139–42

- [44] Joensen P, Frindt R F and Morrison S R 1986 Single-layer MoS2 Mater. Res. Bull. 21 457–61

- [45] Lin ZY et al 2018 Solution-processable 2D semiconductors for high-performance large-area electronics Nature 562 254

- [46] Zheng J, Zhang H, Dong S H, Liu Y P, Nai C T, Shin H S, Jeong H Y, Liu B and Loh K P 2014 High yield exfoliation of two-dimensional chalcogenides using sodium naphthalenide Nat. Commun. 5 2995

- [47] Donley M, Murray P and McDevitt N 1988 Synthesis and characterization of MoS<sub>2</sub> thin films grown by pulsed laser evaporation MRS Proc. 140 277

- [48] Skrabalak S E and Suslick K S 2005 Porous MoS<sub>2</sub> synthesized by ultrasonic spray pyrolysis J. Am. Chem. Soc. 127 9990–1

- [49] Tan L K, Liu B, Teng J H, Guo S, Low H Y and Loh K P 2014 Atomic layer deposition of a MoS $_2$  film Nanoscale 6 10584–8

W Zhu et al

- [50] Das S, Robinson J A, Dubey M, Terrones H and Terrones M 2015 Beyond graphene: progress in novel two-dimensional materials and van der Waals solids *Annu. Rev. Mater. Res.* 45 1–27

- [51] Cao W, Jiang J K, Xie X J, Pal A, Chu J H, Kang J H and Banerjee K 2018 2D layered materials for next-generation electronics: opportunities and challenges *IEEE Trans. Electron Devices* 65 4109–21

- [52] Mas-Ballesté R, Gómez-Navarro C, Gómez-Herrero J and Zamora F 2011 2D materials: to graphene and beyond Nanoscale 3 20–30

- [53] Miró P, Audiffred M and Heine T 2014 An atlas of twodimensional materials Chem. Soc. Rev. 43 6537–54

- [54] Butler S Z *et al* 2013 Progress, challenges, and opportunities in two-dimensional materials beyond graphene *Acs Nano* 7 2898–926

- [55] Fiori G, Bonaccorso F, Iannaccone G, Palacios T, Neumaier D, Seabaugh A, Banerjee S K and Colombo L 2014 Electronics based on two-dimensional materials Nat. Nanotechnol. 9768

- [56] Jariwala D, Sangwan V K, Lauhon L J, Marks T J and Hersam M C 2014 Emerging device applications for semiconducting two-dimensional transition metal dichalcogenides Acs Nano 8 1102–20

- [57] Avouris P, Heinz T F and Low T 2017 2D Materials: Properties and Devices (Cambridge: Cambridge University Press)

- [58] Seabaugh A and Lake R 2003 Tunnel diodes *Digital Encyclopedia of Applied Physics* (New York: Wiley)

- [59] Thomas P et al 2015 Performance evaluation of  $In_{0.53}Ga_{0.47}As$ Esaki tunnel diodes on silicon and InP substrates *IEEE Trans*. Electron Devices 62 2450–6

- [60] Majumdar K et al 2014 Mapping defect density in MBE grown In<sub>0.53</sub>Ga<sub>0.47</sub>As epitaxial layers on Si substrate using Esaki diode valley characteristics IEEE Trans. Electron Devices 61 2049–55

- [61] Pawlik D et al 2012 Benchmarking and Improving III–V Esaki diode performance with a record 2.2 MA cm<sup>-2</sup> peak current density to enhance TFET drive current 2012 IEEE Int. Electron Devices Meeting (IEDM)

- [62] Zhu K G, Wang W, Shao Q Y, Zhao D N, Lu Y F and Ianno N 2011 Self-assembled ordered arrays of nanoscale germanium Esaki tunnel diodes *Appl. Phys. Lett.* **98** 173110

- [63] Fung W Y, Chen L and Lu W 2011 Esaki tunnel diodes based on vertical Si–Ge nanowire heterojunctions Appl. Phys. Lett. 99 092108

- [64] Oehme M, Hahnel D, Werner J, Kaschel M, Kirfel O, Kasper E and Schulze J 2009 Si Esaki diodes with high peak to valley current ratios Appl. Phys. Lett. 95 242109

- [65] Wernersson L E, Kabeer S, Zela V, Lind E, Zhao J, Yan Y, Seifert W and Seabaugh A 2003 A combined UHV-CVD and rapid thermal diffusion process for SiGe Esaki diodes by ultra shallow junction formation *Int. Semiconductor Device Research* Symp. (10–12 December 2003) pp 164–5

- [66] El Kazzi S et al 2015 Staggered band gap  $n^+In_{0.5}Ga_{0.5}As/p^+GaAs_{0.5}Sb_{0.5}$  Esaki diode investigations for TFET device predictions J. Cryst. Growth 424 62–7

- [67] Yan R S et al 2015 Esaki diodes in van der Waals heterojunctions with broken-gap energy band alignment Nano Lett. 15 5791–8

- [68] Roy T, Tosun M, Cao X, Fang H, Lien D H, Zhao P D, Chen Y Z, Chueh Y L, Guo J and Javey A 2015 Dual-gated MoS<sub>2</sub>/WSe<sub>2</sub> van der Waals tunnel diodes and transistors *Acs Nano* 9 2071–9

- [69] Shim J et al 2016 Phosphorene/rhenium disulfide heterojunction-based negative differential resistance device for multi-valued logic Nat. Commun. 7 13413

- [70] Xu K, Cai Y H and Zhu W J 2018 Esaki diodes based on 2D/3D heterojunctions *IEEE Trans. Electron Devices* **65** 4155–9

- [71] Krishnamoorthy S, Lee E W, Lee C H, Zhang Y W, McCulloch W D, Johnson J M, Hwang J, Wu Y Y and Rajan S 2016 High current density 2D/3D MoS<sub>2</sub>/GaN Esaki tunnel diodes Appl. Phys. Lett. 109 183505

- [72] Britnell L, Gorbachev R V, Geim A K, Ponomarenko L A, Mishchenko A, Greenaway M T, Fromhold T M, Novoselov K S and Eaves L 2013 Resonant tunnelling and negative differential conductance in graphene transistors Nat. Commun. 4 1794

- [73] Zhao P, Feenstra R M, Gu G and Jena D 2013 SymFET: a proposed symmetric graphene tunneling field-effect transistor IEEE Trans. Electron Devices 60 951–7

- [74] Fallahazad B et al 2015 Gate-tunable resonant tunneling in double bilayer graphene heterostructures Nano Lett. 15 428–33

- [75] Kang S et al 2015 Bilayer graphene-hexagonal boron nitride heterostructure negative differential resistance interlayer tunnel FET IEEE Electron Device Lett. 36 405–7

- [76] Lin Y C et al 2015 Atomically thin resonant tunnel diodes built from synthetic van der Waals heterostructures Nat. Commun. 67311

- [77] Ozcelik V O, Azadani J G, Yang C, Koester S J and Low T 2016 Band alignment of two-dimensional semiconductors for designing heterostructures with momentum space matching *Phys. Rev.* B 94 035125

- [78] Majumdar A, Wang X L, Kumar A, Holt J R, Dobuzinsky D, Venigalla R, Ouyang C, Koester S J and Haensch W 2009 Gate length and performance scaling of undoped-body extremely thin SOI MOSFETs IEEE Electron Device Lett. 30 413–5

- [79] Lu W-Y and Taur Y 2006 On the scaling limit of ultrathin SOI MOSFETs IEEE Trans. Electron Devices 53 1137–41

- [80] Yu X, Kang J, Takenaka M and Takagi S 2017 Evaluation of mobility degradation factors and performance improvement of ultrathin-body germanium-on-insulator MOSFETs by GOI thinning using plasma oxidation *IEEE Trans. Electron Devices* 64 1418–25

- [81] Low T, Li M F, Samudra G, Yeo Y C, Zhu C X, Chin A and Kwong D L 2005 Modeling study of the impact of surface roughness on silicon and germanium UTB MOSFETs IEEE Trans. Electron Devices 52 2430–9

- [82] Ohashi T, Takahashi T, Beppu N, Oda S and Uchida K 2011 Experimental evidence of increased deformation potential at MOS interface and its impact on characteristics of ETSOI FETs 2011 Int. Electron Devices Meeting (5–7 December 2011) pp 16.4.1–4

- [83] Low T, Li M F, Fan W J, Ng S T, Yeo Y C, Zhu C, Chin A, Chan L and Kwong D L 2004 Impact of surface roughness on silicon and germanium ultra-thin-body MOSFETs IEEE Int. Electron Devices Meeting 2004 Technical Digest pp 151–4

- [84] Radisavljevic B and Kis A 2013 Mobility engineering and a metal-insulator transition in monolayer MoS<sub>2</sub> Nat. Mater. 12 815–20

- [85] Liu L T, Lu Y and Guo J 2013 On monolayer MoS<sub>2</sub> field-effect transistors at the scaling limit *IEEE Trans. Electron Devices* 60 4133–9

- [86] Cao W, Kang J H, Sarkar D, Liu W and Banerjee K 2015 2D semiconductor FETs-projections and design for sub-10 nm VLSI IEEE Trans. Electron Devices 62 3459–69

- [87] Liu H, Neal A T and Ye P D D 2012 Channel length scaling of MoS<sub>2</sub> MOSFETs Acs Nano 6 8563–9

- [88] Zhu W J, Low T, Lee Y H, Wang H, Farmer D B, Kong J, Xia F N and Avouris P 2014 Electronic transport and device prospects of monolayer molybdenum disulphide grown by chemical vapour deposition Nat. Commun. 5 3087

- [89] Zhu Y B et al 2018 Monolayer molybdenum disulfide transistors with single-atom-thick gates Nano Lett. 18 3807–13

- [90] Yang L, Lee R, Papa Rao S, Tsai W and Ye P D 2015 10 nm nominal channel length  $MoS_2$  FETs with EOT 2.5 nm and 0.52 mA  $\mu$ m<sup>-1</sup> drain current 2015 73rd Annual Device Research Conf. (DRC) pp 237–8

- [91] Desai S B  $et\,al\,2016\,MoS_2$  transistors with 1-nanometer gate lengths Science 354 99–102

- [92] Castellanos-Gomez A 2015 Black phosphorus: narrow gap wide applications *J. Phys. Chem. Lett.* 6 4280–91

- [93] Allain A, Kang J H, Banerjee K and Kis A 2015 Electrical contacts to two-dimensional semiconductors *Nat. Mater.* 14 1195–205

- [94] Das S, Chen HY, Penumatcha AV and Appenzeller J 2013 High performance multilayer MoS<sub>2</sub> transistors with scandium contacts Nano Lett. 13 100–5

- [95] Chuang S et al 2014 MoS<sub>2</sub> P-type transistors and diodes enabled by high work function MoO<sub>x</sub> contacts Nano Lett. 14 1337–42

- [96] Yang L M et al 2014 Chloride molecular doping technique on 2D materials: WS<sub>2</sub> and MoS<sub>2</sub> Nano Lett. 14 6275–80

- [97] Fang H, Tosun M, Seol G, Chang T C, Takei K, Guo J and Javey A 2013 Degenerate n-doping of few-layer transition metal dichalcogenides by potassium *Nano Lett.* 13 1991–5

- [98] Du Y C, Liu H, Neal A T, Si M W and Ye P D 2013 Molecular doping of multilayer MoS<sub>2</sub> field-effect transistors: reduction in sheet and contact resistances *IEEE Electron Device Lett.* 34 1328–30

- [99] Kappera R, Voiry D, Yalcin S E, Branch B, Gupta G, Mohite A D and Chhowalla M 2014 Phase-engineered lowresistance contacts for ultrathin MoS<sub>2</sub> transistors Nat. Mater. 13 1128–34

- [100] Leong W S, Luo X, Li Y D, Khoo K H, Quek S Y and Thong J T L 2015 Low resistance metal contacts to MoS<sub>2</sub> devices with nickel-etched-graphene electrodes Acs Nano 9,869–77

- [101] Yu L L et al 2014 Graphene/MoS<sub>2</sub> hybrid technology for large-scale two-dimensional electronics *Nano Lett.* 14 3055–63

- [102] Liu Y et al 2015 Toward barrier free contact to molybdenum disulfide using graphene electrodes Nano Lett. 15 3030–4

- [103] Cui X et al 2015 Multi-terminal transport measurements of  $MoS_2$  using a van der Waals heterostructure device platform Nat. Nanotechnol. 10 534

- [104] Kaasbjerg K, Martiny J H J, Low T and Jauho A-P 2017 Symmetry-forbidden intervalley scattering by atomic defects in monolayer transition-metal dichalcogenides *Phys. Rev.* B 96 241411

- [105] Liu T, Liu S, Tu K H, Schmidt H, Chu L, Xiang D, Martin J, Eda G, Ross C A and Garaj S 2019 Crested two-dimensional transistors Nat. Nanotechnol. 14 223–6

- [106] Kim S et al 2012 High-mobility and low-power thin-film transistors based on multilayer MoS<sub>2</sub> crystals Nat. Commun. 3 1011

- [107] Qiu H et al 2013 Hopping transport through defect-induced localized states in molybdenum disulphide Nat. Commun. 4 2642

- [108] Lai R et al 2007 Sub 50 nm InP HEMT device with Fmax greater than 1 THz 2007 IEEE Int. Electron Devices Meeting (10–12 December 2007) pp 609–11

- [109] Lin Y-M, Dimitrakopoulos C, Jenkins K A, Farmer D B, Chiu H-Y, Grill A and Avouris P 2010 100 GHz transistors from Wafer-scale epitaxial graphene Science 327 662

- [110] Wu Y, Lin Y-m, Bol A A, Jenkins K A, Xia F, Farmer D B, Zhu Y and Avouris P 2011 High-frequency scaled graphene transistors on diamond-like carbon *Nature* 472 74

- [111] Wu Y et al 2012 State-of-the-art graphene high-frequency electronics Nano Lett. 12 3062–7

- [112] Liao L, Lin Y-C, Bao M, Cheng R, Bai J, Liu Y, Qu Y, Wang K L, Huang Y and Duan X 2010 High-speed graphene transistors with a self-aligned nanowire gate *Nature* 467 305

- [113] Lin Y-M et al 2011 Wafer-scale graphene integrated circuit Science 332 1294–7

- [114] Krasnozhon D, Lembke D, Nyffeler C, Leblebici Y and Kis A 2014 MoS<sub>2</sub> transistors operating at gigahertz frequencies Nano Lett. 14 5905–11

- [115] Cheng R, Jiang S, Chen Y, Liu Y, Weiss N, Cheng H C, Wu H, Huang Y and Duan X F 2014 Few-layer molybdenum disulfide transistors and circuits for high-speed flexible electronics Nat. Commun. 5 5143

- [116] Theis T N and Solomon P M 2010 In Quest of the 'next switch': prospects for greatly reduced power dissipation in a successor to the silicon field-effect transistor *Proc. IEEE* 98 2005–14

- [117] Seabaugh A C and Qin Z 2010 Low-voltage tunnel transistors for beyond CMOS logic *Proc. IEEE* **98** 2095–110

- [118] Ionescu A M and Riel H 2011 Tunnel field-effect transistors as energy-efficient electronic switches *Nature* 479 329–37

- [119] Lattanzio L, De Michielis L and Ionescu A M 2011 Electronhole bilayer tunnel FET for steep subthreshold swing and improved ON current Solid-State Device Research Conf.

- (ESSDERC) 2011 Proc. of the European (12–16 September 2011) pp 259–62

- [120] Lattanzio L, De Michielis L and Ionescu A M 2012 Complementary germanium electron—hole bilayer tunnel FET for sub-0.5 V operation *IEEE Electron Device Lett*. 33 167–9

- [121] Guangle Z et al 2012 Novel gate-recessed vertical InAs/GaSb TFETs with record high ION of 180  $\mu$ A  $\mu$ m<sup>-1</sup> at VDS = 0.5 V Electron Devices Meeting (IEDM) 2012 IEEE Int. (10–13 December 2012) pp 32.6.1–4

- [122] Britnell L et al 2012 Field-effect tunneling transistor based on vertical graphene heterostructures Science 335 947–50

- [123] Hao L and Seabaugh A 2014 Tunnel field-effect transistors: state-of-the-art *IEEE J. Electron Devices Soc.* **2** 44–9

- [124] Tomioka K, Yoshimura M and Fukui T 2012 Steep-slope tunnel field-effect transistors using III–V nanowire/ Si heterojunction 2012 IEEE Symp. on VLSI Technology (Piscataway, NJ, USA, 12–14 June 2012) (Piscataway, NJ: IEEE) pp 47–8

- [125] Mohata D K et al 2011 Demonstration of MOSFET-like on-current performance in arsenide/antimonide tunnel FETs with staggered hetero-junctions for 300 mV logic applications Electron Devices Meeting (IEDM) 2011 IEEE Int. (5–7 December 2011) pp 33.5.1–4

- [126] Ilatikhameneh H, Tan Y H, Novakovic B, Klimeck G, Rahman R and Appenzeller J 2015 Tunnel field-effect transistors in 2D transition metal dichalcogenide materials IEEE J. Explor. Solid-State Comput. Devices Circuits 1 12–8

- [127] Ghosh R K and Mahapatra S 2013 Monolayer transition metal dichalcogenide channel-based tunnel transistor IEEE J. Electron Devices 1 175–80

- [128] Zhang Q, Iannaccone G and Fiori G 2014 Two-dimensional tunnel transistors based on  $Bi_2Se_3$  thin film *IEEE Electron Device Lett.* 35 129–31

- [129] Szabo A, Koester S J and Luisier M 2015 Ab initio simulation of van der Waals MoTe<sub>2</sub>–SnS<sub>2</sub> heterotunneling FETs for lowpower electronics IEEE Electron Device Lett. 36 514–6

- [130] Li M O, Esseni D, Nahas J J, Jena D and Xing H G 2015 Twodimensional heterojunction interlayer tunneling field effect transistors (thin-TFETs) IEEE J. Electron Devices 3 200-7

- [131] Lu S C, Mohamed M and Zhu W J 2016 Novel vertical heteroand homo-junction tunnel field-effect transistors based on multi-layer 2D crystals 2D Mater. 3 011010

- [132] Roy T, Tosun M, Hettick M, Ahn G H, Hu C M and Javey A 2016 2D–2D tunneling field-effect transistors using WSe<sub>2</sub>/ SnSe<sub>2</sub> heterostructures Appl. Phys. Lett. 108 083111

- [133] Sarkar D, Xie X J, Liu W, Cao W, Kang J H, Gong Y J, Kraemer S, Ajayan P M and Banerjee K 2015 A subthermionic tunnel field-effect transistor with an atomically thin channel Nature 526 91–5

- [134] Agnihotri P, Dhakras P and Lee J U 2016 Bipolar junction transistors in two-dimensional WSe<sub>2</sub> with large current and photocurrent gains *Nano Lett.* **16** 4355–60

- [135] Lin CY *et al* 2017 Atomic-monolayer two-dimensional lateral quasi-heterojunction bipolar transistors with resonant tunneling phenomenon *Acs Nano* 11 11015–23

- [136] Lee G, Pearton S J, Ren F and Kim J 2018 2D material-based vertical double heterojunction bipolar transistors with high current amplification Adv. Electron. Mater. 5 1800745

- [137] Kim J, Mastro M A, Tadjer M J and Kim J 2018 Heterostructure WSe<sub>2</sub>—Ga<sub>2</sub>O<sub>3</sub> junction field-effect transistor for low-dimensional high-power electronics ACS Appl. Mater. Interfaces 10 29724—9

- [138] Lim J Y et al 2018 Van der Waals junction field effect transistors with both n- and p-channel transition metal dichalcogenides NPJ 2D Mater. Appl. 2 37

- [139] Shin H G et al 2018 Vertical and in-plane current devices using NbS<sub>2</sub>/n-MoS<sub>2</sub> van der Waals Schottky junction and graphene contact Nano Lett. 18 1937–45

- [140] Wang H, Yu L L, Lee Y H, Shi Y M, Hsu A, Chin M L, Li L J, Dubey M, Kong J and Palacios T 2012 Integrated circuits based on bilayer MoS<sub>2</sub> transistors *Nano Lett.* **12** 4674–80

- [141] Yu C, Fan M, Yu K, Hu V P, Su P and Chuang C 2016 Evaluation of monolayer and bilayer 2D transition metal dichalcogenide devices for SRAM applications *IEEE Trans. Electron Devices* 63 625–30

- [142] Kshirsagar C U, Xu W, Su Y, Robbins M C, Kim C H and Koester S J 2016 Dynamic memory cells using MoS<sub>2</sub> fieldeffect transistors demonstrating femtoampere leakage currents *Acs Nano* 10 8457–64

- [143] Bertolazzi S, Krasnozhon D and Kis A 2013 Nonvolatile memory cells based on MoS<sub>2</sub>/graphene heterostructures Acs Nano 7 3246–52

- [144] Cao W, Kang J, Bertolazzi S, Kis A and Banerjee K 2014 Can 2D-nanocrystals extend the lifetime of floating-gate transistor based nonvolatile memory? *IEEE Trans. Electron* Devices 61 3456–64

- [145] Choi M S, Lee G H, Yu Y J, Lee D Y, Lee S H, Kim P, Hone J and Yoo W J 2013 Controlled charge trapping by molybdenum disulphide and graphene in ultrathin heterostructured memory devices Nat. Commun. 4 1624

- [146] Lipatov A, Sharma P, Gruverman A and Sinitskii A 2015 Optoelectrical molybdenum disulfide (MoS2)-ferroelectric memories Acs Nano 9 8089–98

- [147] Yap W C, Jiang H, Liu J L, Xia Q F and Zhu W J 2017 Ferroelectric transistors with monolayer molybdenum disulfide and ultra-thin aluminum-doped hafnium oxide Appl. Phys. Lett. 111 013103

- [148] Si M W, Liao P Y, Qiu G, Duan Y Q and Ye P D D 2018 Ferroelectric field-effect transistors based on MoS<sub>2</sub> and CuInP<sub>2</sub>S<sub>6</sub> two-dimensional van der Waals heterostructure *Acs Nano* 12 6700–5

- [149] Wang M et al 2018 Robust memristors based on layered twodimensional materials Nat. Electron. 1 130–6

- [150] Ge R J, Wu X H, Kim M, Shi J P, Sonde S, Tao L, Zhang Y F, Lee J C and Akinwande D 2018 Atomristor: nonvolatile resistance switching in atomic sheets of transition metal dichalcogenides Nano Lett. 18 434–41

- [151] Lankhorst M H, Ketelaars B W and Wolters R A 2005 Low-cost and nanoscale non-volatile memory concept for future silicon chips Nat. Mater. 4 347–52

- [152] Wong H S P, Raoux S, Kim S, Liang J L, Reifenberg J P, Rajendran B, Asheghi M and Goodson K E 2010 Phase change memory *Proc. IEEE* 98 2201–27

- [153] Zhou Y and Ramanathan S 2015 Mott memory and neuromorphic devices Proc. IEEE 103 1289–310

- [154] Sung J H et al 2017 Coplanar semiconductor-metal circuitry defined on few-layer MoTe<sub>2</sub> via polymorphic heteroepitaxy Nat. Nanotechnol. 12 1064

- [155] Li W B and Li J 2016 Ferroelasticity and domain physics in two-dimensional transition metal dichalcogenide monolayers Nat. Commun. 7 10843

- [156] Duerloo K A N and Reed E J 2016 Structural phase transitions by design in monolayer alloys Acs Nano 10 289–97

- [157] Zhang C *et al* 2016 Charge mediated reversible metalinsulator transition in monolayer MoTe<sub>2</sub> and  $W_xMo_{1-x}Te_2$  alloy *Acs Nano* 10 7370–5

- [158] Li Y, Duerloo K A, Wauson K and Reed E J 2016 Structural semiconductor-to-semimetal phase transition in twodimensional materials induced by electrostatic gating *Nat. Commun.* 7 10671

- [159] Wang Y et al 2017 Structural phase transition in monolayer MoTe<sub>2</sub> driven by electrostatic doping Nature 550 487–91

- $[160] \ Zhang F, Zhang H R, Krylyuk S, Milligan C A, Zhu Y Q, \\ Zemlyanov D Y, Bendersky L A, Burton B P, Davydov A V and \\ Appenzeller J 2019 Electric-field induced structural transition in vertical MoTe_2- and Mo_{1-x}W_xTe_2-based resistive memories \\ \textit{Nat. Mater. 18} 55$

- [161] Rehn DA, Li Y, Pop E and Reed EJ 2018 Theoretical potential for low energy consumption phase change memory utilizing electrostatically-induced structural phase transitions in 2D materials NPJ Comput. Mater. 4 2

- [162] Tosun M, Chuang S, Fang H, Sachid A B, Hettick M, Lin Y J, Zeng Y P and Javey A 2014 High-gain inverters based on WSe<sub>2</sub> complementary field-effect transistors Acs Nano 8 4948–53

- [163] Yu L L, Zubair A, Santos E J G, Zhang X, Lin Y X, Zhang Y H and Palacios T 2015 High-performance WSe<sub>2</sub> complementary metal oxide semiconductor technology and integrated circuits Nano Lett. 15 4928–34

- [164] Wachter S, Polyushkin D K, Bethge O and Mueller T 2017 A microprocessor based on a two-dimensional semiconductor Nat. Commun. 8 14948

- [165] Yu W J, Li Z, Zhou H L, Chen Y, Wang Y, Huang Y and Duan X F 2013 Vertically stacked multi-heterostructures of layered materials for logic transistors and complementary inverters Nat. Mater. 12 246–52

- [166] Cho A J, Park K C and Kwon J Y 2015 A high-performance complementary inverter based on transition metal dichalcogenide field-effect transistors *Nanoscale Res. Lett.* 10 115

- [167] Pezeshki A, Shokouh S H H, Jeon P J, Shackery I, Kim J S, Oh I K, Jun S C, Kim H and Im S 2016 Static and dynamic performance of complementary inverters based on nanosheet alpha-MoTe<sub>2</sub> p-channel and MoS<sub>2</sub> n-channel transistors *Acs Nano* 10 1118–25

- [168] Sedighi B, Hu X S, Nahas J J and Niemier M 2014 Nontraditional computation using beyond-CMOS tunneling devices IEEE J. Emerg. Sel. Top. Circuits Syst. 4438–49

- [169] Dreslinski R G et al 2013 Centip3De: a 64-core 3D stacked near-threshold system *IEEE Micro* 33 8–16

- [170] Yang R, Li H, Smithe K K H, Kim T R, Okabe K, Pop E, Fan J A and Wong H P 2017 2D molybdenum disulfide (MoS<sub>2</sub>) transistors driving RRAMs with 1T1R configuration 2017 IEEE Int. Electron Devices Meeting (IEDM) (2–6 December 2017) pp 19.5.1–4

- [171] Iqbal M W, Iqbal M Z, Khan M F, Shehzad M A, Seo Y, Park J H, Hwang C and Eom J 2015 High-mobility and airstable single-layer WS<sub>2</sub> field-effect transistors sandwiched between chemical vapor deposition-grown hexagonal BN films Sci. Rep. 5 10699

- [172] Liu W, Kang J, Sarkar D, Khatami Y, Jena D and Banerjee K 2013 Role of metal contacts in designing high-performance monolayer n-type WSe<sub>2</sub> field effect transistors *Nano Lett*. 13 1983–90

- [173] Wang X et al 2014 Chemical vapor deposition growth of crystalline monolayer MoSe<sub>2</sub> Acs Nano 8 5125–31

- [174] Chen J et al 2017 Chemical vapor deposition of large-size monolayer MoSe<sub>2</sub> crystals on Molten glass J. Am. Chem. Soc. 139 1073–6

- [175] Liu W, Sarkar D, Kang J, Cao W and Banerjee K 2015 Impact of contact on the operation and performance of back-gated monolayer MoS<sub>2</sub> field-effect-transistors Acs Nano 9 7904–12

- [176] Schmidt M, Lemme M C, Gottlob H D B, Driussi F, Selmi L and Kurz H 2009 Mobility extraction in SOI MOSFETs with sub 1 nm body thickness *Solid-State Electron*. 53 1246–51

- [177] Granzner R, Polyakov V M, Schippel C and Schwierz F 2014 Empirical model for the effective electron mobility in silicon nanowires *IEEE Trans. Electron Devices* 61 3601–7

- [178] Wang H, Wang X, Xia F, Wang L, Jiang H, Xia Q, Chin M L, Dubey M and Han S-J 2014 Black phosphorus radiofrequency transistors Nano Lett. 14 6424–9

- [179] Zhu W, Park S, Yogeesh M N, McNicholas K M, Bank S R and Akinwande D 2016 Black phosphorus flexible thin film transistors at gighertz frequencies *Nano Lett.* 16 2301–6

2D Mater. **6** (2019) 032004 W Zhu et al

[180] Feng Z H, Yu C, Li J, Liu Q B, He Z Z, Song X B, Wang J J and Cai S J 2014 An ultra clean self-aligned process for high maximum oscillation frequency graphene transistors *Carbon* 75 249–54

- [181] Guo Z et al 2013 Record maximum oscillation frequency in C-face epitaxial graphene transistors Nano Lett. 13 942–7

- [182] Schwierz F 2013 Graphene transistors: status prospects and problems *Proc. IEEE* 101 1567–84

- [183] Lemme M and Schwierz F 2016 Graphene for RF analogue applications 2D Materials for Nanoelectronics (Boca Raton, FL: CRC) pp 79–106

- [184] Sun L, Qin G X, Seo J H, Celler G K, Zhou W D and Ma Z Q 2010 12 GHz thin-film transistors on transferrable silicon

- nanomembranes for high-performance flexible electronics  $Small\, {\color{red} 6}\, 2553-7$

- [185] Seo J, Ling T, Guo L J and Ma Z 2016 Fast flexible thinfilm transistors with deep submicron channel enabled by nanoimprint lithography 2016 IEEE Radio and Wireless Symp. (RWS) (24–27 January 2016) pp 162–4

- [186] Su L Y and Huang J J 2015 Demonstration of radio-frequency response of amorphous IGZO thin film transistors on the glass substrate *Solid-State Electron*. **104** 122–5