## **ARTICLE**

Received 29 Aug 2013 | Accepted 27 Nov 2013 | Published 17 Jan 2014

DOI: 10.1038/ncomms4087

# Electronic transport and device prospects of monolayer molybdenum disulphide grown by chemical vapour deposition

Wenjuan Zhu<sup>1,\*</sup>, Tony Low<sup>1,\*</sup>, Yi-Hsien Lee<sup>2</sup>, Han Wang<sup>1</sup>, Damon B. Farmer<sup>1</sup>, Jing Kong<sup>3</sup>, Fengnian Xia<sup>4</sup> & Phaedon Avouris<sup>1</sup>

Layered transition metal dichalcogenides display a wide range of attractive physical and chemical properties and are potentially important for various device applications. Here we report the electronic transport and device properties of monolayer molybdenum disulphide grown by chemical vapour deposition. We show that these devices have the potential to suppress short channel effects and have high critical breakdown electric field. However, our study reveals that the electronic properties of these devices are at present severely limited by the presence of a significant amount of band tail trapping states. Through capacitance and ac conductance measurements, we systematically quantify the density-of-states and response time of these states. Because of the large amount of trapped charges, the measured effective mobility also leads to a large underestimation of the true band mobility and the potential of the material. Continual engineering efforts on improving the sample quality are needed for its potential applications.

<sup>&</sup>lt;sup>1</sup> IBM Thomas J. Watson Research Center, Yorktown Heights, New York 10598, USA. <sup>2</sup> Department of Materials Science and Engineering, National Tsing Hua University, Hsinchu 30013, Taiwan. <sup>3</sup> Department of Electrical Engineering and Computer Sciences, Massachusetts Institute of Technology, Boston, Massachusetts 02139, USA. <sup>4</sup> Department of Electrical Engineering, Yale University, New Haven, Connecticut 06511, USA. \* These authors contributed equally to the work. Correspondence and requests for materials should be addressed to W.Z. (email: wenjuan@us.ibm.com) or to F.X. (email: fengnian.xia@yale.edu).

wo-dimensional materials are attracting considerable attention due to their unique electronic, optical and mechanical properties<sup>1</sup>. Following the success of graphene, a group of 2D materials known as the transition metal dichalcogenides (TMDs) has begun to garner attention. Among them, molybdenum disulphide (MoS<sub>2</sub>) is probably one of the most explored TMDs<sup>2,3</sup>. The sizeable (1.8 eV) direct band gap of monolayer MoS<sub>2</sub> (ref. 4) makes it a potential material for not only digital electronics but also numerous photonic applications such as light emitter<sup>5</sup>, photodetectors<sup>6,7</sup> and solar cells<sup>8</sup>. Excellent mechanical flexibility of MoS<sub>2</sub> also makes it a compelling semiconducting material for flexible electronics<sup>9,10</sup>. Most existing studies and device demonstrations were performed on exfoliated MoS<sub>2</sub> flakes<sup>11-19</sup>. In particular, field-effect-transistors based on monolayer MoS<sub>2</sub> was found to exhibit high on/off ratios of  $\sim 10^8$ , steep subthreshold swing of  $\sim 70^{\circ}$  mV dec<sup>-1</sup> (refs 18,20), with reported electron effective mobility ranging from 1 to  $480 \,\mathrm{cm}^2 \,\mathrm{V}^{-1} \,\mathrm{s}^{-1}$  (refs 14,17,20-26) depending on the device structures, dielectric environment and processing<sup>21,27</sup>. These encouraging early reports coupled with continual engineering efforts<sup>28</sup> present a compelling case for monolayer MoS2 as an alternative to traditional organic material or amorphous silicon for low-end applications with basic requirement of an effective mobility of  $> 30 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  (ref. 20) for example, high resolution displays and photodetection<sup>6,7</sup>.

Recently, the advent of mass production technologies has enabled scalable growth of polycrystalline monolayer MoS<sub>2</sub> by chemical vapour deposition (CVD)<sup>29-32</sup>, hence providing a commercially viable path towards MoS2 electronics at low cost<sup>33</sup>. However, the mobility of CVD MoS<sub>2</sub> is typically much lower than its exfoliated counterpart, with reported values in the range of 5 to  $22 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  (refs 34-36). The physical origin of the differences between CVD and exfoliated MoS2 is not clear at present; however, structural defects<sup>37</sup> such as vacancies, dislocations, grain boundaries as well as charged interfacial states due to the dielectrics in contact<sup>14</sup> can be responsible for the degradation in mobility. Although this problem has presented a major hurdle to the realization of wafer-scale MoS<sub>2</sub> electronics and photonics, systematic studies of it are very few<sup>35</sup>. Very recently, the MoS<sub>2</sub> community realized that there are technical difficulties to achieve accurate mobility extraction due to the role of contacts and fringing capacitive contributions<sup>38</sup>. Four-terminal Hall effect measurements are more accurate, but have only been demonstrated at very high carrier densities using an electrolyte gating scheme<sup>26</sup> or at very low temperatures<sup>17</sup>. These Hall measurements were all performed on exfoliated MoS2, and will be more challenging to perform in CVD samples due to significantly larger amount of localized states, as will be discussed in this manuscript.

Here, we present a systematic methodology for characterizing electronic properties of scalable CVD MoS<sub>2</sub>, reporting also the presence of significant amounts of band tail states and their profound impact on the electrical device performance. The density distribution and dynamics of these trap states of CVD MoS<sub>2</sub> are characterized through systematic capacitance and ac conductance measurements. Extraction of basic electronic transport quantities like the mobility edge and effective mobility is performed using four-probe current measurements. Complementary modelling allows us to draw insights into relevant device quantities such as the fractional occupation of band and trap states, band mobility and the anomalous subthreshold slope. Lastly, high-field electrical behaviour such as drain-induced barrier lowering and critical breakdown fields are examined.

#### **Results**

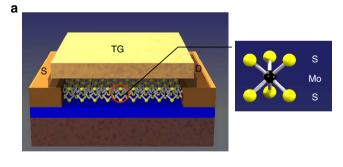

Characterization of monolayer CVD MoS<sub>2</sub>. Monolayer MoS<sub>2</sub> was synthesized by CVD, using solid sulphur (S) and molybdenum oxide (MoO<sub>3</sub>) as the precursors and perylene-3,4,9,10-tetracarboxylic acid tetra-potassium salt (PTAS)<sup>39</sup> as the seed for the CVD growth (see Methods for details). Hall-bar devices were fabricated on these CVD MoS<sub>2</sub> monolayers. Figure 1a illustrated the schematic of the device. The top gate dielectrics are 2 nm aluminium deposited by e-beam evaporation and re-oxidized as a seed layer, followed by 30 nm HfO<sub>2</sub> deposited by atomic layer deposition (ALD). The details of the device process are discussed in Methods. The atomic force microscopy (AFM) image and the step height profile at the boundary of a MoS<sub>2</sub> triangular area are shown in Fig. 1b and the inset of Fig. 1b, respectively. The thickness of the MoS<sub>2</sub> layer is measured to be about 0.8 nm, confirming its monolayer character. The Raman spectrum of the CVD MoS<sub>2</sub> is shown in Supplementary Fig. 1. The E<sub>2g</sub> and A<sub>1g</sub> modes are at around 383 and 403 cm<sup>-1</sup>, respectively. Comparing the peak position with the spectrum obtained from the exfoliated monolayer MoS<sub>2</sub> (ref. 40), we further verify that the MoS<sub>2</sub> film is monolayer.

Density and dynamics of band tail states. At present, the reported values of the electron mobility in CVD-grown MoS<sub>2</sub> devices<sup>34–36</sup> are at least two orders of magnitude smaller than the intrinsic limit<sup>41</sup>, suggesting a high degree of disorder and scattering. An inhomogeneous potential distribution in a semiconductor leads to the smearing of the band edge and the formation of a tail of band gap state<sup>42</sup>. For example, this inhomogeneity could be the result of a random distribution of trapped charges in sulphur vacancies in MoS<sub>2</sub> itself<sup>43</sup> or at MoS<sub>2</sub>-dielectric (SiO<sub>2</sub> or high-k dielectric) interfaces<sup>14</sup>. Structural defects<sup>37</sup>, for example, simple vacancies<sup>43</sup>, dislocations and grain boundaries, would also lead to localized gap states.

Figure 1 | Molybdenum disulphide physical properties and device structure. (a) Schematic of MOSFET with monolayer chemical vapour deposition (CVD) grown molybdenum disulphide (MoS $_2$ ). (b) AFM image of CVD grown MoS $_2$  on SiO $_2$ /Si substrate. The scale bar in the AFM image is 10  $\mu$ m. The inset shows the step height profile of MoS $_2$  in the AFM image.

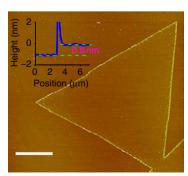

The electronic states in the band tail can be characterized using standard capacitance and ac conductance measurement commonly used in the study of semiconductor devices<sup>44</sup>. Here, these localized states respond like traps with different time constants  $\tau_{it}$  and are electrically equivalent to an additional capacitance and resistance in parallel to the semiconductor capacitance. The gate-to-channel capacitance and resistance were measured on the Hallbars, with high terminal on the top gate and low terminal on the source, drain and all four voltage probing leads simultaneously, as shown in Supplementary Fig. 2. The measured capacitance as a function of frequency is shown in Fig. 2a. The observed double hump feature indicates at least two types of traps with different time constants at a given gate voltage. Herein, we denote these traps by the labels 'M' and 'B', for reasons that will be made

apparent below. The equivalent circuit model of the device is shown in Fig. 2b with total impedance given by:

$$Z = (Y_{itB} + Y_{itM} + i\omega C_s + i\omega C_j)^{-1} + (i\omega C_{ox})^{-1} + r_s$$

(1)

where  $\omega$  is the angular frequency,  $C_s$  is the quantum capacitance of the MoS<sub>2</sub>,  $C_j$  is the parasitic capacitance,  $C_{\rm ox}$  is the oxide capacitance,  $r_s$  is the series resistance,  $Y_{\rm itM}$  and  $Y_{\rm itB}$  are the traps' admittance. Here  $Y_{\rm itB} = [\tau_{\rm itB}/C_{\rm itB} + 1/(i\omega C_{\rm itB})]^{-1}$ , where  $C_{\rm itB}$  and  $\tau_{\rm itB}$  are the capacitance and time constant of trap B. The trap capacitance  $C_{\rm itB}$  is related to the trap density  $D_{\rm itB}$  via the following:  $C_{\rm itB} = eD_{\rm itB}$ , where e is the elementary electric charge. Similar expressions apply to trap M. The measured capacitance in series mode  $C_{\rm ms}$  is related to the imaginary part of the total

**Figure 2** | **Characterization of the density and dynamics of band tail states.** (a) Capacitance as a function of frequency measured at various gate voltages. The device width is 4 μm and length is 44 μm. The symbols are the experimental results and the lines are fittings using the device model shown in (b). (b) The equivalent circuit model of the device, simplified parallel model and the measurement model in series mode. (c) Density and time constant of trap states as a function of gate voltages. The symbols are experimental results extracted from the capacitance  $C_{ms}$  and ac conductance  $G_p$ . The lines are models, see text. (d) Extracted ac conductance over angular frequency  $G_p/ω$  as a function of frequency f at various gate voltages. (e) Parameterized model,  $D_n(E)$ , describing the electronic density-of-states of both the extended and localized states. The valence density-of-state is also included in the illustration using the mirror image of conduction density-of-state. The inset illustrates the band diagram of MoS<sub>2</sub> MOSFET. (f) Multi-frequency capacitance of MoS<sub>2</sub> Hall-bar as a function of gate voltage. The symbols are experimental results and the lines are the modelling results.

impedance Z by the following formula:

$$C_{\rm ms} = -\frac{1}{\omega * {\rm Im}[Z]}.$$

(2)

The lines in Fig. 2a are the fits using this model. We can see that the model provides an excellent fit to the experimental data. From the fitting, we can extract the density of traps and their time constant as a function of gate voltage, shown in Fig. 2c. Here, we observe that traps 'M' and 'B' are populated predominately within the 'mid-gap' and 'band edge' regions, respectively.

Alternatively, the density and time constant of the traps can be extracted from the ac conductance  $G_{\rm p}$  (ref. 44). The ac conductance is obtained from the measured capacitance and resistance. The measured resistances as a function of gate voltage at various frequencies are shown in Supplementary Fig. 3. The extraction method of ac conductance are described in more detail in the Supplementary Note 1. The extracted ac conductance over angular frequency  $G_{\rm p}/\omega$  is plotted as function of the driving frequencies f in Fig. 2d. Since the density-of-states of type B traps is several orders of magnitude larger than that of type M in this gate bias range, we expect the former to dominate the ac conductance. The relation between  $G_{\rm p}(\omega)$  and the trap density  $D_{\rm itB}$  is given as the following (ref. 44):

$$\frac{G_{\rm p}(\omega)}{\omega} = \frac{eD_{\rm itB}}{2\omega\tau_{\rm itB}}\ln[1 + (\omega\tau_{\rm itB})^2] \tag{3}$$

from which one can deduce the  $D_{\rm itB}$  and the respective time constant  $\tau_{\rm itB}$  from the following simple relations<sup>44</sup>:

$$D_{\rm itB} = \frac{2.5}{e} \left( \frac{G_{\rm p}}{\omega} \right)_{\rm peak} \tag{4}$$

$$\tau_{\rm itB} = \frac{1.98}{2 \times 3.14 \times f_0}.\tag{5}$$

Here,  $(G_{\rm p}/\omega)_{\rm peak}$  is the maximum  $G_{\rm p}(\omega)/\omega$  value and  $f_0$  is the frequency at which this maximum is obtained. Repeating the above procedure for different top gate voltages  $V_{\rm TG}$  allows us to extract  $D_{\rm itB}(V_{\rm TG})$  and  $\tau_{\rm itB}(V_{\rm TG})$  as shown in Fig. 2c. From Fig. 2c, we see that the density-of-states and time constant of B type traps extracted based on the capacitance and ac conductance are in good agreement.

Below, we present parameterized models for the electronic density-of-states and their time constants fitted to the experiments. We describe the electronic density-of-states of the measured distributed trap states at the band edge (that is, type B) and the extended states with two piece-wise functions as follows:

$$D_{\rm n}(E) = \begin{cases} \alpha D_0 \exp\left[\frac{E - E_{\rm D}}{\varphi}\right] + D_{\rm itM}, & E_{\rm D} - \frac{1}{2}E_{\rm G} < E < E_{\rm D} \\ D_0 - (1 - \alpha)D_0 \exp\left[-\frac{E - E_{\rm D}}{\varphi\prime}\right] + D_{\rm itM}, & E > E_{\rm D} \end{cases}$$

$$(6)$$

and illustrate them in Fig. 2c,e. Here,  $D_0$  is the 2D density-of-states for perfect crystalline MoS<sub>2</sub>, taken to be  $3.3 \times 10^{14}$  eV  $^{-1}$  cm  $^{-2}$ , consistent with an effective mass of  $0.4m_0$  at the conduction band minimum at the K valley for monolayer MoS<sub>2</sub> (ref. 45). Here we ignored contribution from the satellite valley along  $\Gamma$ K with energy 200 meV higher than the conduction band minimum  $^{41,46}$  because the carrier population is insignificant at these energies at our biasing range. Furthermore, our MoS<sub>2</sub> devices are typically n-type doped.  $\varphi$  is the characteristic energy width of the band tail. In the limit of  $\varphi = 0$ ,  $D_n(E)$  becomes a step function as required for perfect 2D crystals with the conduction band edge situated at  $E_D$ .  $\varphi'$  is chosen so that the two piece-wise functions have continuous gradients at  $E_D$ . Solving the electrostatics problem, to be described below, a best-fit to the

experimentally extracted density-of-states yields the parameter set:  $\alpha = 0.33$  and  $\phi = 100\,\mathrm{meV}$ . The comparison between the model  $D_\mathrm{n}(V_\mathrm{TG})$  and the measured band tail states  $D_\mathrm{itB}(V_\mathrm{TG})$  is shown in Fig. 2c, and the mid-gap states  $D_\mathrm{itM}(V_\mathrm{TG})$  is described by an error function instead. The traps' response time is fitted to an exponential model,

$$\tau = \tau_0 \exp\left[-\frac{E - E_{\text{mid}}}{\Phi_{\tau}}\right] \tag{7}$$

and the comparison with experimental data is shown in Fig. 2c. With the parameterized density-of-states model, we can calculate the ac capacitance and compare against experiments. The Poisson equation describing the electrostatics of the problem can be expressed as:

$$Q_{\rm n} + Q_0 = \varepsilon_{\rm ox} \left( \frac{V_{\rm TG} + E_{\rm D}/e}{t_{\rm top}} \right) \tag{8}$$

where  $t_{\rm top}$  is the 'effective-oxide-thickness' for the top gate dielectric,  $\varepsilon_{\rm ox}$  is the dielectric constant of silicon oxide,  $Q_0$  is a constant that includes contributions from the fixed charges and doping in as-prepared MoS<sub>2</sub> and so on, and  $Q_{\rm n}$  is the electronic charges in the smeared out conduction band and can be computed from  $Q_{\rm n}=e\int D_{\rm n}(E)f_{\rm n}(E,E_{\rm F}){\rm d}E$  where  $f_{\rm n}$  is the Fermi Dirac function. In solving for the self-consistent electrostatics described by using equation 8, the Fermi energy  $E_{\rm F}$  is taken to be the reference that is,  $E_{\rm F}=0$ . Once the electrostatics is determined, the admittance associated with each of the traps can then be computed via the following:

$$Y_{\rm it} = e^2 \int D_{\rm it} \frac{j\omega + \omega^2 \tau_{\rm it}}{1 + (\tau_{\rm it}\omega)^2} \frac{\partial f_{\rm n}}{\partial E} dE$$

(9)

and the total capacitance can be computed employing the equivalent circuit model in Fig. 2b and using equations (1) and (2). Reasonable agreement with the measured ac capacitance is obtained as shown in Fig. 2f.

To summarize, the electronic density-of-states model described above is well-calibrated to the experimentally measured density and dynamics of the band tail states. It follows an exponentially decaying behaviour, with a significantly large energy width of  $\varphi=100\,\mathrm{meV}$ , suggesting a high degree of potential disorder and scattering. This model will be employed in the subsequent discussion to obtain other quantities of interest, such as the band mobility.

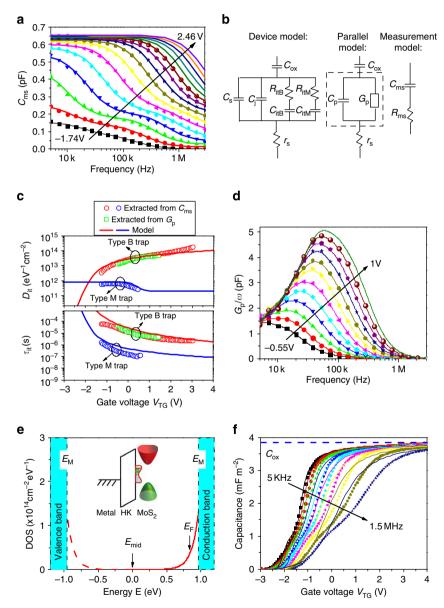

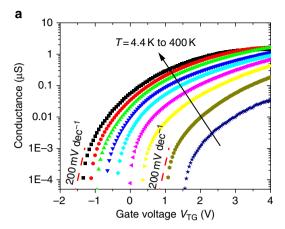

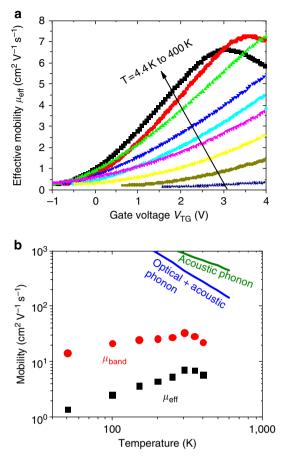

Mobility edge. The concept of a 'mobility edge' has greatly facilitated our understanding of electronic transport in a disordered system<sup>47</sup>. The mobility edge is a boundary located in the band tail, in which states above it are extended states with band transport, while those below it are localized states that conduct via thermally assisted mechanisms such as Mott variable range hopping (VRH)<sup>48-50</sup> or an Arrhenius-type activated behaviour<sup>51</sup>. Four-point variable temperature measurements were performed on our devices from 4.4 to 400 K as shown in Fig. 3a. We found that neither the VRH nor the Arrhenius model can individually describe the data satisfactorily over the whole temperature range. It is very likely that a combination of both transport mechanisms might be operating here. For example, the VRH usually dominates for localized states deep in the band tail, while the Arrhenius-type activated behaviour is more likely for shallow localized states.

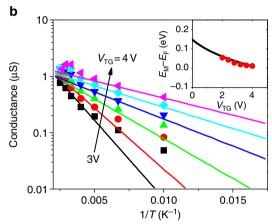

The conductance versus the inverse of temperature (1/T) is shown in Fig. 3b, showing the exponential decrease with 1/T over the intermediate temperature range, where the conductance G

**Figure 3 | Temperature dependence of conductance and activation energy.** (a) Four-point conductance as a function of gate voltage measured at various temperatures from 4.4 to  $400\,\mathrm{K}$  on a  $\mathrm{MoS_2}$  Hall-bar. (b) Conductance as a function of reverse of temperature 1/T at various gate voltages. The inset shows the activation energy at various gate voltages fitted to the Arrhenius-activated energy model. The symbols are experimental results extracted from the conductance; the solid line gives the modeling results. (c) The calculated band carriers as a function of gate voltage at various temperatures.

can be described by:

$$G = G_0 e^{-E_a/k_B T} \tag{10}$$

where  $E_{\rm a}$  is the activation energy,  $k_{\rm B}$  is the Boltzmann constant and  $G_{\rm 0}$  is a fitting parameter. This allows us to extract the activation energy  $E_{\rm a}=E_{\rm M}-E_{\rm F}$ . The measured  $E_{\rm a}$  (versus  $V_{\rm TG}$ ) is compared with the model (see Fig. 3c inset), which allows us to

determine the location of the mobility edge  $E_{\rm M}$  in the energy band picture. We found that in our devices  $E_{\rm M}$  is  $\approx$  0.01 eV above  $E_{\rm D}$ , as illustrated in Fig. 2e. We also noticed a departure from activated behaviour at lower temperature or bias, indicating the possible onset of an additional transport mechanism such as VRH. The extracted activation energy in the inset of Fig. 3b suggests that, in most of our gate biases, the Fermi level does not exceed the mobility edge energy. However, at large  $V_{\rm TG}$  that is,  $V_{\rm TG} > 2V$ , the Fermi energy is within tens of meV from the mobility edge. Hence, one can expect an appreciable fraction of extended states occupation due to thermal smearing. The calculated band carrier densities as a function of gate voltage at various temperatures are shown in Fig. 3c.

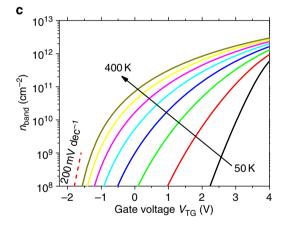

**Transport coefficients**. The 'effective mobility', or sometimes referred to as the 'drift mobility', is a commonly used transport coefficient in semiconductors<sup>52</sup>. It is defined as the ratio of the measured conductivity to the total charge density that is,  $\mu_{\text{eff}}$  =  $\sigma/Q_{\text{total}}$ . The total charge density  $Q_{\text{total}}$  is typically estimated from  $C_{\text{ox}}(V_{\text{g}}-V_{\text{T}})$ , where  $C_{\text{ox}}$  is the oxide capacitance,  $V_{\text{g}}$  is the gate voltage and  $V_{\rm T}$  is the threshold voltage. We extract  $C_{\rm ox}$  from the measured capacitance at strong accumulation. Figure 4a shows the effective mobility as a function of gate voltage at different temperatures. The effective mobility is  $< 10 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  over the range of temperature and applied bias in our experiments. Contact resistance is eliminated in our measurement that employs a four-probe scheme. The measured effective mobility is significantly lower than the phonon-limited intrinsic mobility in monolayer MoS<sub>2</sub>, predicted to be over  $400 \,\mathrm{cm}^2 \,\mathrm{V}^{-1} \,\mathrm{s}^{-1}$ (ref. 41), and the highest measured mobility of  $\sim 200 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  in exfoliated MoS<sub>2</sub> devices<sup>20</sup>. However, it is consistent with results on similar CVD-grown  $MoS_2$  devices that report mobilities in the range of 5 to  $25 \, cm^2 \, V^{-1} \, s^{-1}$  (ref. 35). The significantly lower mobility for CVD-grown MoS<sub>2</sub> is, to a large part, due to the presence of traps.

The total charge density includes both the free and trapped charges:  $Q_{\rm total} = e(n_{\rm loc} + n_{\rm band})$  where  $n_{\rm loc}$  and  $n_{\rm band}$  refer to the density of occupied states below and above the mobility edge, respectively. Another commonly used transport coefficient in a disordered system is the 'band mobility' <sup>53,54</sup>. It is defined as the ratio of the measured conductivity to the density of occupied states above the mobility edge (that is, extended states):

$$\mu_{\text{band}} = \frac{\sigma}{e n_{\text{band}}} = \mu_{\text{eff}} \frac{n_{\text{loc}} + n_{\text{band}}}{n_{\text{band}}}$$

(11)

In general, the density of the extended states is difficult to measure, since the large amount of localized states would result in large noise-to-signal ratio the in the Hall measurement. Up to now, the Hall effect has only been observed in exfoliated  $MoS_2$  with very high carrier density induced by an electrolyte gating scheme<sup>26</sup> or at very low temperatures<sup>17</sup>.

Previously, we obtained  $D_{\rm n}(E)$  in conjunction with  $E_{\rm M}$  in the energy band picture. Solving the electrostatics in conjunction with the above information would allow us to estimate the fraction of localized and extended states. Figure 3c plots the computed  $n_{\rm band}(V_{\rm TG})$  at different temperatures. The result indicates that  $n_{\rm band}$  only accounts for <25% of  $n_{\rm total}$ . Only at high temperature or bias,  $n_{\rm band}$  can exceed 25% that is,  $T>300~{\rm K}$  and  $V_{\rm TG}>2{\rm V}$ . The comparison between the extracted band mobility and measured effective mobility is shown in Fig. 4b. The band mobility is several times higher than the effective mobility, but still significantly lower than the phonon-limited mobility as predicted in ref. 41. This mobility degradation may involve many sources of scattering. For example, structural defects in CVD  ${\rm MoS}_2$  layer and grain boundaries can induce short-range scattering. Surface polar phonon either in the high-k dielectrics

**Figure 4 | Effective mobility and band mobility.** (a) Effective mobility as a function of gate voltage measured at various temperatures in  $MoS_2$  Hall-bar. (b) Effective mobility and the corresponding band mobility as a function of temperature at  $V_{TG} = 4V$ . The mobility limited by  $MoS_2$  phonons scattering based on theoretical calculations<sup>41</sup> are also plotted for comparison.

(HfO $_2$  and AlO $_x$ ) or in the SiO $_2$  substrate underneath can also play a role. However, the significant trap population measured here suggests that Coulomb scattering due to trapped charges is the likely limiting factor for the electron mobility. Because of the parabolic band structure of MoS $_2$ , the energy averaged scattering time due to Coulomb scattering should increase proportionally to temperature $_2^{55}$   $\mu \propto k_B T$ . This is also consistent with the observed trend in Fig. 4b for temperature below 300 K. Above this temperature phonon scattering takes over.

**Subthreshold swing.** In an ideal semiconductor, the subthreshold swing is given by  $^{52}$ :  $S = k_{\rm B} T \ln(10) (1 + C_{\rm D}/C_{\rm ox})$ , where  $C_{\rm D}$  is the depletion capacitance. The subthreshold swing increases linearly with temperature, since the carrier density increases exponentially with temperature  $n \propto \exp\left(\frac{E_{\rm F}-E_{\rm i}}{k_{\rm B}T}\right)$ . In our device, we observed that the subthreshold swing is  $\approx 200 \, {\rm mV} \, {\rm dec}^{-1}$  and nearly independent of temperature, as shown in Fig. 3a. Similar observations were made on MoS<sub>2</sub> flakes 11. This departure from the ideal behaviour can be understood by recalling that the band tail is distributed in energy, that is,  $\exp\left[\frac{E-E_{\rm D}}{\varphi}\right]$ , with an energy width that is significantly larger than the thermal energy that is,  $\phi > > k_{\rm B}T$ . Indeed, the calculated subthreshold behaviour confirms that temperature does not have a significant effect, as shown in Fig. 3c. Hence, the observed temperature-independent

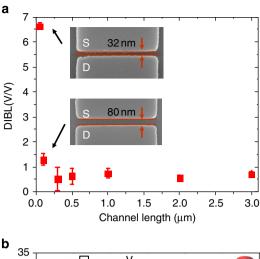

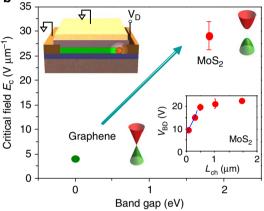

**Figure 5 | Device properties at high electrical fields.** (a) Drain-induced barrier lowering (DIBL) of MOSFET with CVD MoS<sub>2</sub> at various channel lengths. The inset shows the SEM image of the 32 and 80 nm channel length devices. (b) Critical electric field of CVD MoS<sub>2</sub> and graphene. The upper inset shows the measurement configuration. The lower inset shows the lateral breakdown voltage as a function of channel length for MOSFET with CVD MoS<sub>2</sub>.

subthreshold swing reinforced our earlier conclusions on the existence of band tail states.

**Drain-induced barrier lowering**. The electrostatic integrity of an electronic device upon downscaling is often quantified by evaluating the amount of drain-induced barrier lowering (DIBL)<sup>56</sup>. This measures the reduction in threshold voltage due to the applied drain bias. A common approach used to suppress DIBL involves reducing the channel thickness, since the minimum channel length needed to preserve the long channel behaviour is typically  $\sim 4-5$  times the electrostatic scaling length  $\lambda = \sqrt{\epsilon_s t_s t_o x/\epsilon_{ox}}$  for a planar device structure 57,58, where  $\epsilon_s$  and  $\varepsilon_{\rm ox}$  are the dielectric constants of the semiconductor and the gate oxide, and  $t_s$  and  $t_{ox}$  are the thicknesses of the semiconductor and gate oxide, respectively. In this regard, thinner silicon has been pursued by using SOI (silicon-on-insulator) and ETSOI (extremely thin silicon-on-insulator). However, the mobility degrades markedly as the thickness is scaled down due to surface roughness<sup>59,60</sup>. Atomically thin 2D semiconducting material such as MoS2 and WSe2 are promising candidates in this regard. The typical DC performances of MoS<sub>2</sub> MOSFETs with various channel lengths are shown in Supplementary Fig. 4. Figure 5a shows the DIBL of CVD MoS<sub>2</sub> MOSFET with variable channel lengths from 4 µm to 32 nm. Despite the thick dielectric

used in our MOSFETs, ( $\sim$ 34 nm HfO<sub>2</sub>/ AlO<sub>x</sub> stack for the long channel devices,  $\sim$ 60 nm HfO<sub>2</sub>/ AlO<sub>x</sub> for the short channel devices, limited by the bulging of gate dielectrics on the source/ drain side wall), a clear upturn of DIBL is only observed at a channel length of 32 nm. Extrapolating to a device with a 3 nm HfO<sub>2</sub> gate insulator would predict a limiting channel length feature of  $\sim$ 7 nm. Theoretically, for a MOSFET with monolayer MoS<sub>2</sub> (channel thickness:  $\sim$ 0.8 nm, dielectric constant: 6.8  $\sim$ 7.1  $\varepsilon_0$ , where  $\varepsilon_0$  is the vacuum permittivity<sup>61</sup>) and 1 nm equivalent oxide thickness (EOT), the electrostatic scaling length  $\lambda$  is only about 1.2 nm. These considerations suggest that MoS<sub>2</sub> could be a very promising material for scaled, high-density electronics.

Breakdown electric fields. The large band gap of MoS<sub>2</sub> implies the possibility of device operation at higher voltages or electric fields. Figure 5b shows the critical breakdown fields of graphene and CVD MoS<sub>2</sub> MOSFETs devices. The measurement setup is shown on the upper-left inset of Fig. 5b. The channel-length dependence of breakdown voltage of MoS2 MOSFETs is shown in the lower-right inset of Fig. 5b. The critical field can be extracted from the slope of the breakdown voltage versus channel length. Here we extracted the breakdown field from MoS<sub>2</sub> transistors with channel lengths of 80 and 285 nm. (More details about the breakdown test results of MoS2 transistors and graphene transistors are shown in the Supplementary Figs 5 and 6, and Supplementary Notes 2 and 3.) The measured breakdown field of CVD MoS<sub>2</sub> is about five times larger than that of graphene and significantly larger than that of SOI with 100 nm silicon thickness<sup>62</sup>. In this regard, MoS<sub>2</sub> can also be a very promising platform for power devices.

#### **Discussion**

We have systematically studied the electronic transport properties of CVD MoS<sub>2</sub> devices. We report the observation of a significant amount of electronic trap states through capacitance and ac conductance measurements and their impact on the low-field electronic properties of MoS<sub>2</sub> devices. In particular, the measured effective mobility significantly underestimates the band mobility. An anomalous subthreshold behaviour, with distinctive temperature insensitivity, is also accounted for by the presence of these band tail states. We also studied the high-field electronic properties of MoS2 devices and demonstrated the possibility to aggressively scale them down and their high breakdown electric fields. These attractive device attributes present a compelling case for wafer-scale monolayer MoS2 as alternative to organic and other thin film materials for flexible electronics and photonics, including high resolution displays, photo-detection, logic electronics, power devices with solar energy collecting and so on. From the fundamental material stand point, understanding of the microscopic origin of these band tail states is critical for further improvement of the material's electronic properties.

#### Methods

**Fabrication.** Large-scale monolayer  $MoS_2$  was synthesized at 650 C by APCVD using perylene-3,4,9,10-tetracarboxylic acid tetra-potassium salt (PTAS) as the seed on SiO<sub>2</sub>/Si substrate<sup>39</sup>. Sulphur powder and molybdenum oxide ( $MoO_3$ ) were used as the precursors for the synthesis. The  $SiO_2$  thickness was 300 nm. In the Hall-bar and transistor devices, the source/drain contact metal stack consisted of Ti/Au/Ti (5/15/5 nm). The  $MoS_2$  channel was patterned using electron beam lithography and oxygen plasma etching. The top gate dielectric comprised an  $AlO_x/HfO_2$  stack. The  $AlO_x$  was formed by electron beam evaporation of 2 nm of aluminum metal followed by its natural oxidization in air for a few hours. The 30 nm thick  $HfO_2$  layer was formed using atomic layer deposition (ALD) at 170 degrees. The top gate electrode was Ti/Au (5/40 nm).

**Characterization.** The capacitances were measured using Agilent B1500 Semi-conductor Device Analyzer produced by Agilent technology. The temperature

dependence of conductance was measured using cryogenic probestation produced in Lake Shore Cryotronics, Inc. The Raman spectrum was taken using Labram Aramis produced by Horiba Jobin Yvon. Scanning electron microscopy was measured using Leo 1560 produced by Carl Zeiss.

#### References

- Novoselov, K. S. et al. Two-dimensional atomic crystals. Proc. Natl Acad. Sci. USA 102, 10451–10453 (2005).

- Chhowalla, M. et al. The chemistry of two-dimensional layered transition metal dichalcogenide nanosheets. Nat. Chem. 5, 263–275 (2013).

- Hsu, A. et al. Large-area 2-D electronics: materials, technology, and devices. Proc. IEEE 101, 1638–1652 (2013).

- Mak, K. F., Lee, C., Hone, J., Shan, J. & Heinz, T. F. Atomically thin MoS<sub>2</sub>: a new direct-gap semiconductor. *Phys. Rev. Lett.* 105, 136805 (2010).

- Sundaram, R. S. et al. Electroluminescence in single layer MoS<sub>2</sub>. Nano Lett. 13, 1416–1421 (2013).

- Lee, H. S. et al. MoS<sub>2</sub> nanosheet phototransistors with thickness-modulated optical energy gap. Nano Lett. 12, 3695–3700 (2012).

- 7. Yin, Z. et al. Single-layer MoS<sub>2</sub> phototransistors. Acs Nano **6**, 74–80 (2011).

- Dashora, A., Ahuja, U. & Venugopalan, K. Electronic and optical properties of MoS<sub>2</sub> thin films: feasibility for solar cells. *Comput Mater Sci* 69, 216–221 (2013)

- Pu, J. et al. Highly flexible MoS<sub>2</sub> thin-film transistors with ion gel dielectrics. Nano Lett. 12, 4013–4017 (2012).

- Chang, H.-Y. et al. High-performance, highly bendable MoS<sub>2</sub> transistors with high-K dielectrics for flexible low-power systems. Acs Nano 7, 5446–5452 (2013).

- Ayari, A., Cobas, E., Ogundadegbe, O. & Fuhrer, M. S. Realization and electrical characterization of ultrathin crystals of layered transition-metal dichalcogenides. J. Appl. Phys. 101, 014505–014507 (2007).

- Benameur, M. M. et al. Visibility of dichalcogenide nanolayers. Nanotechnology 22, 125706 (2011).

- Buscema, M. et al. Large and tunable photothermoelectric effect in single-layer MoS<sub>2</sub>. Nano Lett. 13, 358–363 (2013).

- Ghatak, S., Pal, A. N. & Ghosh, A. Nature of electronic states in atomically thin MoS<sub>2</sub> field-effect transistors. Acs Nano 5, 7707–7712 (2011).

- Kim, J.-Y., Choi, S. M., Seo, W.-S. & Cho, W.-S. Thermal and electronic properties of exfoliated metal chalcogenides. *Bull Korean Chem. Soc.* 31, 3225–3227 (2010).

- Lembke, D. & Kis, A. Breakdown of high-performance monolayer MoS<sub>2</sub> transistors. Acs Nano 6, 10070–10075 (2012).

- Radisavljevic, B. & Kis, A. Mobility engineering and a metal-insulator transition in monolayer MoS<sub>2</sub>. Nat. Mater. 12, 815–820 (2013).

- Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS<sub>2</sub> transistors. Nat Nano 6, 147–150 (2011).

- Liu, H., Neal, A. T. & Ye, P. D. Channel length scaling of MoS<sub>2</sub> MOSFETs. Acs Nano 6, 8563–8569 (2012).

- Kim, S. et al. High-mobility and low-power thin-film transistors based on multilayer MoS<sub>2</sub> crystals. Nat. Commun. 3, 1011 (2012).

- Bao, W., Cai, X., Kim, D., Sridhara, K. & Fuhrer, M. S. High mobility ambipolar MoS<sub>2</sub> field-effect transistors: Substrate and dielectric effects. *Appl. Phys. Lett.* 102, 042104 (2013).

- Jariwala, D. et al. Band-like transport in high mobility unencapsulated singlelayer MoS<sub>2</sub> transistors. Appl. Phys. Lett. 102, 173107 (2013).

- Li, S.-L. et al. Thickness-dependent interfacial coulomb scattering in atomically thin field-effect transistors. Nano. Lett. 13, 3546–3552 (2013).

- Perera, M. M. et al. Improved carrier mobility in few-layer MoS<sub>2</sub> field-effect transistors with ionic-liquid gating. Acs Nano 7, 4449–4458 (2013).

- Pradhan, N. R. et al. Intrinsic carrier mobility of multi-layered MoS<sub>2</sub> field-effect transistors on SiO<sub>2</sub>. Appl. Phys. Lett. 102, 123105 (2013).

- Zhang, Y., Ye, J., Matsuhashi, Y. & Iwasa, Y. Ambipolar MoS<sub>2</sub> thin flake transistors. Nano Lett. 12, 1136–1140 (2012).

- Qiu, H. et al. Electrical characterization of back-gated bi-layer MoS<sub>2</sub> field-effect transistors and the effect of ambient on their performances. Appl. Phys. Lett. 100, 123104 (2012).

- Das, S., Chen, H.-Y., Penumatcha, A. V. & Appenzeller, J. High performance multilayer MoS<sub>2</sub> transistors with scandium contacts. *Nano Lett.* 13, 100–105 (2013).

- Liu, K.-K. et al. Growth of Large-Area and Highly Crystalline MoS<sub>2</sub> Thin Layers on Insulating Substrates. Nano Lett. 12, 1538–1544 (2012).

- Najmaei, S. et al. Vapour phase growth and grain boundary structure of molybdenum disulphide atomic layers. Nat. Mater. 12, 754–759 (2013).

- Lee, Y.-H. et al. Synthesis of large-area MoS<sub>2</sub> atomic layers with chemical vapor deposition. Adv. Mater. 24, 2320–2325 (2012).

- Zhan, Y., Liu, Z., Najmaei, S., Ajayan, P. M. & Lou, J. Large-Area vapor-phase growth and characterization of MoS<sub>2</sub> atomic layers on a SiO<sub>2</sub> substrate. Small. 8, 966–971 (2012).

- 33. Wang, H. et al. in IEEE International Electron Devices Meeting (IEDM) 4.6.1–4.6.4 (San Francisco, CA, 2012).

- Amani, M. et al. Electrical performance of monolayer MoS<sub>2</sub> field-effect transistors prepared by chemical vapor deposition. Appl. Phys. Lett. 102, 193107 (2013).

- Liu, H. et al. Statistical Study of deep submicron dual-gated field-effect transistors on monolayer chemical vapor deposition molybdenum disulfide films. Nano Lett. 13, 2640–2646 (2013).

- Wu, W. et al. High mobility and high on/off ratio field-effect transistors based on chemical vapor deposited single-crystal MoS<sub>2</sub> grains. Appl. Phys. Lett. 102, 142106 (2013).

- 37. Zhou, W. *et al.* Intrinsic structural defects in monolayer molybdenum disulfide. *Nano Lett.* **13**, 2615–2622 (2013).

- Fuhrer, M. S. & Hone, J. Measurement of mobility in dual-gated MoS<sub>2</sub> transistors. Nat. Nano 8, 146–147 (2013).

- Lee, Y.-H. et al. Synthesis and transfer of single-layer transition metal disulfides on diverse surfaces. Nano Lett. 13, 1852–1857 (2013).

- Li, S.-L. et al. Quantitative Raman spectrum and reliable thickness identification for atomic layers on insulating substrates. Acs Nano 6, 7381–7388 (2012).

- 41. Kaasbjerg, K., Thygesen, K. S. & Jacobsen, K. W. Phonon-limited mobility in n-type single-layer MoS<sub>2</sub> from first principles. *Phys. Rev. B* **85**, (2012).

- 42. Pollak, M. & Shklovskii, B. Hopping Transport in Solids Vol. 28 (Elsevier Science Publishers B.V., 1991).

- 43. Qiu, H. et al. Hopping transport through defect-induced localized states in molybdenum disulphide. Nat. Commun. 4, 2642 (2013).

- 44. Nicollian, E. H. & Brews, J. R. MOS (metal oxide semiconductor) Physics and Technology (Wiley-Interscience Publication, 1982).

- Shi, H., Pan, H., Zhang, Y.-W. & Yakobson, B. I. Quasiparticle band structures and optical properties of strained monolayer MoS<sub>2</sub> and WS<sub>2</sub>. Phys. Rev.B 87, 155304 (2013).

- Lebègue, S. & Eriksson, O. Electronic structure of two-dimensional crystals from ab initio theory. Phys. Rev. B 79, 115409 (2009).

- 47. Mott, N. F. & Davis, E. A. Electronic Processes in Non-crystalline Materials (Oxford Press, 1979).

- Mott, N. F. Conduction in non-crystalline materials. *Philos Mag.* 21, 863–867 (1969).

- Monroe, D. Hopping in exponential band tails. Phys. Rev. Lett. 54, 146–149 (1985)

- Bässler, M. S. H. Calculation of energy relaxation and transit time due to hopping in an exponential band tail. *Phil. Mag. Lett.* 56, 109–112 (1987).

- Tiedje, T. & Rose, A. A physical interpretation of dispersive transport in disordered semiconductors. Solid State Commun. 37, 49–52 (1981).

- 52. Hori, T. Gate Dielectrics and MOS ULSIs Principles, Technologies, and Applications (Springer, 1997).

- Salleo, A. et al. Intrinsic hole mobility and trapping in a regioregular poly(thiophene). Phys. Rev. B 70, 115311 (2004).

- Völkel, A. R., Street, R. A. & Knipp, D. Carrier transport and density of state distributions in pentacene transistors. *Phys. Rev. B* 66, 195336 (2002).

- Ferry, D. Transport in Nanostructure Vol. 2 (Cambridge University Press, 2009).

- Yuan Taur, T. H. N. Fundamentals of Modern VLSI Devices (Cambridge University Press, 1998).

- Ran-Hong, Y., Ourmazd, A. & Lee, K. F. Scaling the Si MOSFET: from bulk to SOI to bulk. *IEEE Trans. Electron Devices* 39, 1704–1710 (1992).

- Majumdar, A., Zhibin, R., Koester, S. J. & Haensch, W. Undoped-body extremely thin SOI MOSFETs with back gates. *IEEE Trans. Electron Devices* 56, 2270–2276 (2009).

- Low, T. et al. Modeling study of the impact of surface roughness on silicon and Germanium UTB MOSFETs. IEEE Trans. Electron Devices 52, 2430–2439 (2005).

- Ohashi, T., Takahashi, T., Beppu, N., Oda, S. & Uchida, K. in *IEEE International Electron Devices Meeting (IEDM)* 16.14.11–16.14.14 (Washington, DC, 2011).

- Salmani-Jelodar, M., Yaohua, T. & Klimeck, G. in International Semiconductor Device Research Symposium (ISDRS) 1–2 (College Park, MD, 2011).

- Merchant, S. et al.in Proceedings of the 3rd International Symposium on Power Semiconductor Devices and ICs, 1991 (ISPSD '91), 31–35 (Baltimore, MD).

### **Acknowledgements**

We thank Bruce Ek, Jim Bucchignano and Simon Dawes for their contributions to device fabrication. We also thank Jin Cai and Vasili Perebeinos in IBM, Xiao Sun and Prof. Tso-Ping Ma at Yale University and Prof. Mingfu Li at Fudan University for valuable discussions.

#### **Author contributions**

W.Z. and F.X. initiated the project. Y.-H.L. and J.K. carried out CVD MoS<sub>2</sub> growth. W.Z., F.X. and H.W. contributed to device design and fabrication. W.Z. performed the electrical characterization. W.Z., T.I., and F.X. Analysed the data. T.L. performed the modelling. D.B.F. grew the ALD gate dielectric. Y.-H.L. carried out Atomic force spectroscopy (AFM). W.Z. performed Scanning electron spectroscopy (SEM) and Raman spectrum measurement. W.Z. designed, fabricated and measured the graphene devices. P.A. supervised this project. All authors participated in writing of the paper.

#### **Additional information**

$\textbf{Supplementary Information} \ accompanies \ this \ paper \ at \ http://www.nature.com/nature \ communications$

Competing financial interests: The authors declare no competing financial interests.

Reprints and permission information is available online at http://npg.nature.com/reprintsandpermissions/

**How to cite this article:** Zhu, W. *et al.* Electronic transport and device prospects of monolayer molybdenum disulphide grown by chemical vapour deposition. *Nat. Commun.* 5:3087 doi: 10.1038/ncomms4087 (2014).