## Ferroelectric transistors with monolayer molybdenum disulfide and ultra-thin aluminum-doped hafnium oxide

Wui Chung Yap, Hao Jiang, Jialun Liu, Qiangfei Xia, and Wenjuan Zhu

Citation: Appl. Phys. Lett. 111, 013103 (2017); doi: 10.1063/1.4991877

View online: https://doi.org/10.1063/1.4991877

View Table of Contents: http://aip.scitation.org/toc/apl/111/1

Published by the American Institute of Physics

## Articles you may be interested in

Ferroelectricity in hafnium oxide thin films

Applied Physics Letters 99, 102903 (2011); 10.1063/1.3634052

Enhancing ferroelectricity in dopant-free hafnium oxide

Applied Physics Letters 110, 022903 (2017); 10.1063/1.4973928

Understanding ferroelectric Al:HfO<sub>2</sub> thin films with Si-based electrodes for 3D applications

Journal of Applied Physics 121, 204103 (2017); 10.1063/1.4984068

Ferroelectric and piezoelectric properties of Hf<sub>1-x</sub>Zr<sub>x</sub>O<sub>2</sub> and pure ZrO<sub>2</sub> films

Applied Physics Letters 110, 182905 (2017); 10.1063/1.4983031

Stabilizing the ferroelectric phase in doped hafnium oxide

Journal of Applied Physics 118, 072006 (2015); 10.1063/1.4927805

Pulse wake-up and breakdown investigation of ferroelectric yttrium doped HfO<sub>2</sub>

Journal of Applied Physics 121, 154102 (2017); 10.1063/1.4981893

## **MANAGER'S GUIDE**

Accelerate R&D with Multiphysics Simulation

## Ferroelectric transistors with monolayer molybdenum disulfide and ultra-thin aluminum-doped hafnium oxide

Wui Chung Yap, <sup>1</sup> Hao Jiang, <sup>2</sup> Jialun Liu, <sup>1</sup> Qiangfei Xia, <sup>2</sup> and Wenjuan Zhu <sup>1</sup> Department of Electrical and Computer Engineering, University of Illinois at Urbana-Champaign, Urbana,

Illinois 61801, USA

<sup>2</sup>Electrical and Computer Engineering, University of Massachusetts at Amherst, Amherst, Massachusetts 01003, USA

(Received 14 January 2017; accepted 23 June 2017; published online 6 July 2017)

In this letter, we demonstrate ferroelectric memory devices with monolayer molybdenum disulfide (MoS<sub>2</sub>) as the channel material and aluminum (Al)-doped hafnium oxide (HfO<sub>2</sub>) as the ferroelectric gate dielectric. Metal-ferroelectric-metal capacitors with 16 nm thick Al-doped HfO<sub>2</sub> are fabricated, and a remnant polarization of  $3 \mu \text{C/cm}^2$  under a program/erase voltage of 5 V is observed. The capability of potential 10 years data retention was estimated using extrapolation of the experimental data. Ferroelectric transistors based on embedded ferroelectric HfO<sub>2</sub> and MoS<sub>2</sub> grown by chemical vapor deposition are fabricated. Clockwise hysteresis is observed at low program/erase voltages due to slow bulk traps located near the 2D/dielectric interface, while counterclockwise hysteresis is observed at high program/erase voltages due to ferroelectric polarization. In addition, the endurances of the devices are tested, and the effects associated with ferroelectric materials, such as the wake-up effect and polarization fatigue, are observed. Reliable writing/reading in  $MoS_2/Al$ -doped HfO<sub>2</sub> ferroelectric transistors over  $2 \times 10^4$  cycles is achieved. This research can potentially lead to advances of two-dimensional (2D) materials in low-power logic and memory applications. Published by AIP Publishing. [http://dx.doi.org/10.1063/1.4991877]

A ferroelectric dielectric is a polar dielectric in which the polarization can be switched between two or more stable states by the application of an electric field. Ferroelectric random access memory (FRAM) utilizes ferroelectric polarization switching for data storage. In a FRAM cell, the dipoles tend to align themselves with the field direction when an external electric field is applied to the dielectric structure. The dipoles retain their polarization state after the electric field is removed. Therefore, FRAM is ideally non-volatile. Among non-volatile memories, FRAM consumes much less read/write power than magnetoresistive RAM (MRAM) and phasechange RAM (PCRAM), and has better endurance than resistive RAM (RRAM).<sup>2–4</sup> While spin-transfer torque magnetic random-access memory (STT-RAM or STT-MRAM) has the advantage of lower power consumption, the amount of current needed to reorient the magnetization is at present too high for most commercial applications.<sup>5</sup>

Traditional ferroelectric materials are primarily complex perovskites, such as lead zirconate titanate (PZT), strontium bismuth tantalate (SBT), and lead magnesium niobate-lead titanate (PMN-PT).<sup>6,7</sup> FRAMs based on complex perovskites have demonstrated superior energy efficiency and endurance.<sup>8,9</sup> However, these traditional ferroelectric materials have limited thickness scaling and are not compatible with CMOS processes, making them difficult to be adopted in the semiconductor industry. In the last few years, doped metal oxides, including hafnium oxide (HfO<sub>2</sub>) and zirconium oxide (ZrO<sub>2</sub>), were found to possess a ferroelectric phase. 10-19 Ferroelectric HfO<sub>2</sub> has the advantages of a high coercive field, excellent scalability (down to 2.5 nm), and good compatibility with CMOS processing. 16,18,20,21

HfO<sub>2</sub> and ZrO<sub>2</sub> doped with silicon (Si), 10,22-24 yttrium (Y), 12 aluminum (Al), 13 gadolinium (Gd), 14 strontium (Sr), 15 and lanthanum (La)<sup>16</sup> have been confirmed to possess a ferroelectric phase. The phase transitions in these metal oxides were found to be very sensitive to capping layers and substrates, which determine the internal stresses of the film and crystalline phases. The phase transition is also very sensitive to film composition and annealing temperature. For Al-doped HfO<sub>2</sub>, a high annealing temperature (ranging between 650 and 1000 °C) is required to realize the phase transition. 13 FRAMs based on Al-doped HfO<sub>2</sub> on silicon have shown excellent endurance and retention. 16 However, to further scale down the ferroelectric transistors, an ultrathin body in the semiconductor channel is needed. Twodimensional materials can address this issue—the atomically thin body of 2D materials can effectively suppress the so-called short-channel effect. Graphene, transition metal dichalcogenides (TMDCs), and black phosphorus (BP) have been investigated intensively over the past few years. Particularly, graphene and MoS<sub>2</sub> based on traditional ferroelectric materials, including PZT, SBT, and PMN-PT, have been shown to possess promising memory windows.<sup>25–30</sup> However, memories based on 2D materials and ferroelectric HfO<sub>2</sub> hybrid stacks are still unrealized.

In this paper, we demonstrate ferroelectric transistors based on Al-doped HfO2 and monolayer MoS2. To characterize the ferroelectricity of the Al-doped HfO2, we fabricated ferroelectric capacitors with TiN electrodes and 16 nm HfO2 doped with Al. A remnant polarization of  $3 \mu \text{C/cm}^2$  is observed at a 5 V programming voltage. 10-year retention of the ferroelectric Al-doped HfO<sub>2</sub> is demonstrated. Consequently, ferroelectric transistors with embedded Al-doped HfO2 and monolayer MoS2 channel are fabricated, followed by the systematic characterization of the hysteresis effect and endurance of the transistors. Additionally, wake-up and fatigue effects were observed during the endurance test.

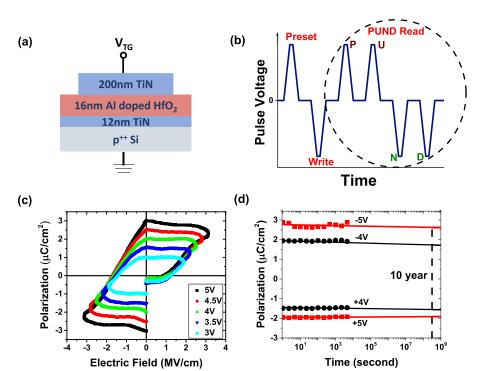

The structure of the ferroelectric capacitors with Al-doped  $HfO_2$  is shown in Fig. 1(a). The  $16\,\mathrm{nm}$   $HfO_2$  with  $5.9\,\mathrm{mol}$ . % Al was deposited via atomic layer deposition (ALD) and annealed at  $1000\,^{\circ}\mathrm{C}$  for 1 s to induce ferroelectricity in the insulator material. The details of the capacitor fabrication are in the supplementary material.

The polarization of the capacitors was measured using the positive-up-negative-down (PUND) method. The capacitors are subjected to a series of five pulses consisting of a preset pulse, a positive switching pulse, a positive non-switching pulse, a negative switching pulse and a negative non-switching pulse, as illustrated in Fig. 1(a). The preset pulse set the ferroelectric  $HfO_2$  in negative spontaneous polarization  $-P_s$  state. The first positive pulse applied (P) will switch the polarization vector into the  $+P_s$  state and the displacement current for this "switching" pulse is<sup>31</sup>

$$i_s(t) = \frac{\partial D}{\partial t} = \frac{\partial (\epsilon E + P)}{\partial t},$$

(1)

where P is the polarization due to the ferroelectric dipoles, E is the electric field, and  $\epsilon$  is the dielectric constant of the dielectric. Since the film has already been polarized positively  $+P_s$ , applying the second positive pulse (U) will not switch the polarization, and the displacement current for this "non-switching" pulse is

$$i_{ns}(t) = \frac{\partial(\epsilon E)}{\partial t}.$$

(2)

The difference between the two currents is therefore given by

$$\Delta i(t) = i_s(t) - i_{ns}(t) = \frac{\partial P(t)}{\partial t}.$$

(3)

The polarization can then be extracted from  $P(t) = \int_0^t \Delta i(t) dt$ . The change in current as a function of time was measured

using a Keithley semiconductor parameter analyzer (model 4200-SCS) equipped with a 4225-PMU ultra-fast I-V module. Figure 1(b) shows the extracted polarization as a function of electric field in various voltage ranges for a capacitor annealed at  $1000\,^{\circ}\text{C}$  for 1 s. A clear hysteresis loop is observed, indicating the formation of the ferroelectric phase in this Al-doped HfO<sub>2</sub>. The remnant polarization was seen to increase monotonically with the program/erase voltage. At 5 V program/erase voltages, the remnant polarizations reach  $3\,\mu\text{C/cm}^2$ , indicating ferroelectricity in these Al-doped HfO<sub>2</sub> dielectrics.

The retention characteristics of the ferroelectric capacitors were also measured. Figure 1(d) shows the polarization as a function of retention time for a capacitor with an area of  $8.1 \times 10^{-5}$  cm<sup>2</sup>. The program/erase pulses are  $\pm 5$  V and  $\pm 4$  V, with a 1  $\mu$ s rise/fall time and a 0.1  $\mu$ s pulse width. The polarization was measured using the PUND method. We can see that the polarization is nearly unchanged with time for the range we have tested (up to 4600 s). The solid lines are the fitting of the experimental results. From the results, we can extrapolate that more than 89% of the original polarization still remains after 10 years.

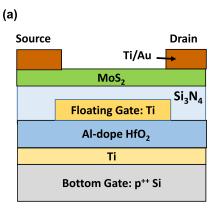

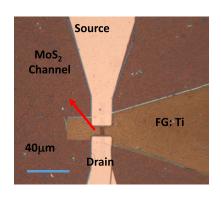

Ferroelectric transistors with monolayer  $MoS_2$  and  $Aldoped\ HfO_2$  were fabricated. The device structure is shown in Fig. 2(a), and an optical image of the device is shown in the inset of Fig. 2(b). The channel width is 3  $\mu$ m, and the channel length is 7.8  $\mu$ m. These transistors have an inverted gate structure, i.e., the gate and ferroelectric gate dielectrics are embedded under the  $MoS_2$  channel. Since the high temperature annealing of the  $HfO_2$  film is needed to convert the film into the ferroelectric phase, forming the ferroelectric gate dielectric prior to transferring the  $MoS_2$  can minimize the thermal budget and the potential damage to the  $MoS_2$ . The device fabrication is detailed in the supplementary material. The DC characteristics of these devices were systematically measured. Here, we use degenerated  $p^+$  silicon and the Ti layer as the bottom gate.

FIG. 1. Ferroelectric Al-doped HfO<sub>2</sub> capacitors. (a) Device structure of the HfO<sub>2</sub> capacitors. (b) Pulse sequence in the PUND measurements (c) Polarization versus electric field (PE) loop of the ferroelectric HfO2 capacitor from PUND measurements. The capacitor area is  $2.02 \times 10^{-5}$  cm<sup>2</sup>. The rise/ fall times are  $1 \mu s$ . The pulse width and delay between pulses are  $0.1 \,\mu s$ . (d) Retention measurements of the ferroelectric HfO2 capacitors. The capacitor area is  $8.1 \times 10^{-5}$  cm<sup>2</sup>. The program and erase pulses are  $\pm 5 \,\mathrm{V}$  and  $\pm 4 \,\mathrm{V}$ with a  $0.1 \,\mu s$  pulse width. The symbols are measured experimental data and the solid lines are the fittings.

(b)

FIG. 2.  $MoS_2$  transistors with ferroelectric  $HfO_2$  gate dielectrics. (a) Device structure of the  $MoS_2$  transistor with embedded ferroelectric  $HfO_2$  gate dielectrics. (b) Optical image of the  $MoS_2$  ferroelectric transistor.

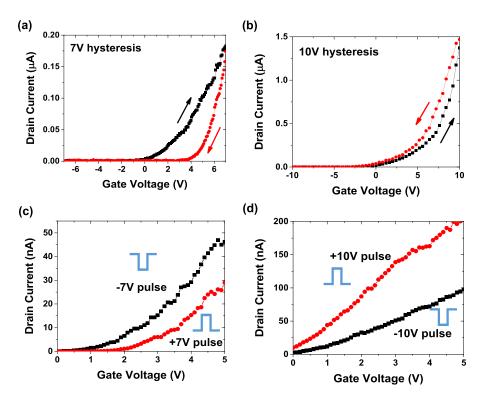

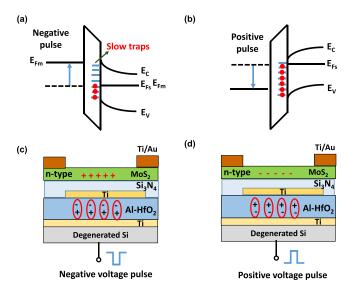

The hysteresis effects of the MoS<sub>2</sub> ferroelectric transistors are shown in Figs. 3(a) and 3(b). A clockwise hysteresis is observed when the gate voltage sweep is in the small voltage range (7 V), and counterclockwise when the gate voltage sweep is in the large voltage range (10 V). A similar trend is also observed in the  $I_D \sim \, V_G$  characteristics after program and erase pulses, shown in Figs. 3(c) and 3(d). Here, the pulse width is 5  $\mu$ s, and the pulse amplitudes are  $\pm 7$  V [Fig. 3(c)] and  $\pm 10 \text{ V}$  [Fig. 3(d)]. At low program/erase voltages (e.g., 7 V), the I<sub>D</sub>V<sub>G</sub> shifts in the positive direction after a positive gate pulse, corresponding to a clockwise hysteresis loop, while at high program/erase voltages (10 V), the I<sub>D</sub>V<sub>G</sub> shifts in the negative direction instead after a positive gate pulse, corresponding to a counterclockwise hysteresis loop in the double gate voltage sweep measurements. These phenomena can be explained by the two competing mechanisms that influence the threshold voltages: charge trapping and ferroelectric polarization switching. At low program/erase voltages, if the electric field in the Al-doped HfO2 is lower than the coercive field, then the program/erase voltage is not high enough to switch the polarization of the dipoles, so charge trapping phenomenon dominates. Figures 4(a) and

4(b) illustrates the impact of the slow bulk traps on the threshold voltage shift. A positive pulse will cause the energy band of the semiconductor at the gate dielectric/semiconductor interface to bend downward, resulting in more bulk traps located close to the interface to move below the Fermi-level, which tend to capture electrons. A negative gate pulse will bend the band upward and cause more slow traps to move above the Fermi-level and release electrons. This will increase the threshold voltage after the positive gate pulse and decrease it after the negative gate pulse, which is consistent with the experimental observation at low program/erase voltages as shown in Fig. 3(c). At high program/ erase voltages, if the electric field in HfO<sub>2</sub> is higher than the coercive field, the program and erase voltage will switch the polarization in HfO<sub>2</sub> film. Figures 4(c) and 4(d) illustrate the impact of ferroelectric switching on the threshold voltage shift. A negative pulse will switch the polarization vector to a  $-P_s$  state, which will induce positive charges in the MoS<sub>2</sub> channel and increase the threshold voltage. A positive pulse will switch the polarization vector in  $HfO_2$  to a  $+P_s$  state, which will induce negative charges in the MoS<sub>2</sub> channel and result in a decrease in the threshold voltage. This is

FIG. 3.  $I_D \sim V_G$  hysteresis and  $I_D \sim V_G$ characteristics after program/erase gate pulses on MoS2 transistors with 16 nm Al doped HfO2. The drain bias is 1V. The channel width and length are  $3 \mu m$ and 7.8  $\mu$ m, respectively. (a)  $I_D \sim V_G$ hysteresis with a back gate voltage sweep between 0 V and 7 V, showing a clockwise hysteresis loop. (b)  $I_D \sim V_G$ hysteresis with a back gate voltage sweep between 0 V and 10 V, showing counterclockwise hysteresis loop. (c) I<sub>D</sub>  $\sim V_G$  characteristics after  $\pm 7 \, V$  program/erase gate pulses.  $I_D \sim V_G$  curve shifts to the positive gate voltage direction after +7 V pulse, indicating charge trapping of slow gap states in the gate dielectrics. (d)  $I_D \sim V_G$  characteristics after ±10 V program/erase gate pulses.  $I_D \sim V_G \, \text{curve}$  shifts to the positive gate voltage direction after +10 V pulse, indicating that ferroelectric polarization switching is dominant.

FIG. 4. (a) and (b) illustrate the impact of slow traps on the hysteresis of the transistors. (a) A negative gate pulse and (b) a positive gate pulse are applied on the gate. (c) and (d) illustrate the influence of ferroelectric polarization switching in Al-doped HfO<sub>2</sub> on the hysteresis of the transistors. (c) When a negative pulse is applied on the gate, the polarization vector in HfO<sub>2</sub> will be switched to  $-P_s$  state, which will induce positive charges in the MoS<sub>2</sub> channel and result in an increase in threshold voltage. (d) When a positive voltage pulse is applied on the gate, the polarization vector in HfO<sub>2</sub> will be switched to  $+P_s$  state, which will induce negative charges in the MoS<sub>2</sub> channel and result in a decrease in threshold voltage.

consistent with the experimental observations at high program/erase voltages as shown in Fig. 3(d). The fact that a ferroelectric memory window was observed with a counterclockwise loop at 10 V program/erase voltage indicates that ferroelectricity is dominant over charge trapping at high program/erase voltages. In this device, the silicon nitride thickness is 25 nm, and the HfO<sub>2</sub> thickness is 16 nm. The dielectric constant for silicon nitride is around 6.5, and the dielectric constant for HfO<sub>2</sub> is around 20.<sup>32,33</sup> If the coercive field in HfO<sub>2</sub> is 1 MV/cm [based on the polarization versus electric field (PE) measured in the capacitors], we would expect the minimum gate voltage required to change the polarization in HfO<sub>2</sub> to be 9.3 V. This is consistent with our experimental observation that the ferroelectric counterclockwise hysteresis loop is observed only at the high program/ erase voltage (10 V), but not at the low program/erase voltage (7 V). The current leakage across the dielectric layer was monitored to ensure that there is no significant current tunneling of charge carriers into the floating gate.

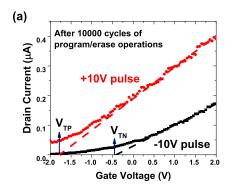

An important criterion for nonvolatile memory devices is the long-term endurance, i.e., how many program/erase cycles it can sustain before it becomes unreliable. For ferroelectric memory devices, this translates to the long-term stability of the switchable polarization states.<sup>34</sup> The endurance of the MoS<sub>2</sub> ferroelectric transistors were tested with program/erase voltages of  $\pm 10 \,\mathrm{V}$  and pulse width of  $5 \,\mu\mathrm{s}$ . Figure 5(a) shows the drain current as a function of gate voltage for a MoS<sub>2</sub> ferroelectric transistor after 10 000 cycles of program/erase operations. The threshold voltages of the MoS<sub>2</sub> ferroelectric transistors after the positive and negative gate pulses,  $V_{TP}$  and  $V_{TN}$ , were extracted by the linear fitting of the I<sub>D</sub>V<sub>G</sub> curves at high fields. The threshold voltage difference between these two states,  $\Delta V_T = V_{TN} - V_{TP}$ , was plotted as a function of program/erase cycles, shown in Fig. 5(b). As the number of program/erase operation increases,  $\Delta V_T$  first increases (up to 1000 cycles) and then starts to decrease. The widening of the memory window at the early stage is due to the "wake-up" effect, while the shrinking of the memory window after 1000 cycles is attributed to the fatigue effect of the ferroelectric materials. Two stages of polarization change have been reported not only in conventional lead zirconate titanate (PZT) materials but also ferroelectric HfO<sub>2</sub>. 35,36 The "wake-up effect" corresponds to the initial increase in the number of switchable polarization domains, resulting in the widening of the ferroelectric memory window. Explanations such as domain wall de-pinning have been offered to account for this effect. The second effect, "Polarization fatigue," corresponds to degradation in the polarization states after a high number of switching states.<sup>34</sup> All of the devices demonstrated counterclockwise cycle loops, indicating that they are ferroelectric.

In summary, we have demonstrated ferroelectric transistors based on monolayer  $MoS_2$  and ultra-thin ferroelectric Aldoped  $HfO_2$ . Ferroelectric capacitors with  $16 \text{ nm } HfO_2$  doped with Al show a remnant polarization of  $3 \mu C/cm^2$  under a program/erase voltage of 5 V. The retention measurements of the ferroelectric  $HfO_2$  capacitors show that more than 89% of the original polarization remains after 10 years. Ferroelectric transistors based on embedded ferroelectric hafnium oxide and molybdenum disulfides grown by chemical vapor deposition

FIG. 5. Endurance measurements of the  $MoS_2$  ferroelectric transistors. (a)  $I_DV_G$  characteristics of the transistor after  $10\,000$  cycles of program/erase operations. The drain voltage is  $1\,V$ . The channel width and length are  $3\,\mu m$  and  $7.8\,\mu m$ , respectively. The threshold voltages of the  $MoS_2$  ferroelectric transistors after positive and negative pulses,  $V_{TP}$  and  $V_{TN}$ , are extracted by the linear fitting of the  $I_DV_G$  curves at high fields. (b) The difference of the threshold voltages after negative and positive pulses,  $\Delta V_T = V_{TN} - V_{TP}$ , as a function of program/erase cycles.

were then fabricated, and the hysteresis and endurance of the ferroelectric transistors were studied. At low program/erase voltages, clockwise hysteresis was observed due to charge trapping of slow interface states, while at high program/erase voltages, counterclockwise hysteresis was observed due to ferroelectric polarization switching. We demonstrate reliable writing/reading in MoS<sub>2</sub>/Al-doped HfO<sub>2</sub> ferroelectric transistors over  $2 \times 10^4$  cycles. In the endurance test, the wake-up effect was detected at an early stage of the program/erase cycles and fatigue effect was observed in the late stages of the cycles, which is a characteristic behavior of ferroelectric materials. These ferroelectric transistors can open up a path to extend the scaling of ferroelectric memory.

See supplementary material for the fabrication of ferroelectric Al-doped HfO<sub>2</sub> capacitors and ferroelectric MoS<sub>2</sub> transistors.

The authors at UIUC would like to acknowledge NSF support under Grant No. ECCS 16-53241 CAR. Work at UMass Amherst was supported in part by the U.S. Air Force Office of Scientific Research (AFOSR) under Grant No. FA9550-12-1-0038.

- <sup>1</sup>T. C. Xu and V. Leppanen, "Analysing emerging memory technologies for big data and signal processing applications," in 5th International Conference on Digital Information Processing and Communications (ICDIPC) (2015), pp. 104-109.

- <sup>2</sup>C. H. Cheng, C. Y. Tsai, A. Chin, and F. S. Yeh, "High performance ultralow energy RRAM with good retention and endurance," in International Electron Devices Meeting (2010).

- <sup>3</sup>C. H. Cheng, A. Chin, and F. S. Yeh, "Novel ultra-low power RRAM with good endurance and retention," in IEEE Symposium on VLSI Technology (2010), pp. 85-86.

- <sup>4</sup>K. Kim and S. Y. Lee, "Memory technology in the future," Microelectron. Eng. 84, 1976-1981 (2007).

- <sup>5</sup>D. C. Ralph and M. D. Stiles, "Spin transfer torques," J. Magn. Magn. Mater. 320, 1190-1216 (2008).

- <sup>6</sup>N. Setter, D. Damjanovic, L. Eng, G. Fox, S. Gevorgian, S. Hong, A. Kingon, H. Kohlstedt, N. Y. Park, G. B. Stephenson, I. Stolitchnov, A. K. Taganstev, D. V. Taylor, T. Yamada, and S. Streiffer, "Ferroelectric thin films: Rev. materials, properties, applications," J. Appl. Phys. 100, 051606

- <sup>7</sup>Y. Xu, Ferroelectric Materials and Their Applications (Elsevier, 1991).

- <sup>8</sup>J. Rodriguez, J. Rodriguez-Latorre, C. Zhou, A. Venugopal, A. Acosta, M. Ball, P. Ndai, S. Madan, H. McAdams, K. R. Udayakumar, S. Summerfelt, T. San, and T. Moise, "180 nm FRAM reliability demonstration with ten years data retention at 125 degrees C," in International Reliability Physics Symposium (2013).

- <sup>9</sup>S. Sakai and M. Takahashi, "Recent progress of ferroelectric-gate fieldeffect transistors and applications to nonvolatile logic and FeNAND flash memory," Materials 3, 4950-4964 (2010).

- <sup>10</sup>T. S. Boscke, S. Teichert, D. Brauhaus, J. Muller, U. Schroder, U. Bottger, and T. Mikolajick, "Phase transitions in ferroelectric silicon doped hafnium oxide," Appl. Phys. Lett. 99, 112904 (2011).

- <sup>11</sup>N. Gong, X. Sun, H. Jiang, Q. Xia, and T. P. Ma, in 46th IEEE Semiconductor Interface Specialists Conference (Arlington, VA, 2015).

- <sup>12</sup>J. Müller, U. Schröder, T. S. Böscke, I. Müller, U. Böttger, L. Wilde, J. Sundqvist, M. Lemberger, P. Kücher, T. Mikolajick, and L. Frey, "Ferroelectricity in yttrium-doped hafnium oxide," J. Appl. Phys. 110, 114113 (2011).

- <sup>13</sup>S. Mueller, J. Mueller, A. Singh, S. Riedel, J. Sundqvist, U. Schroeder, and T. Mikolajick, "Incipient ferroelectricity in Al-doped HfO2 thin films," Adv. Funct. Mater. 22, 2412–2417 (2012).

- <sup>14</sup>S. Mueller, C. Adelmann, A. Singh, S. Van Elshocht, U. Schroeder, and T. Mikolajick, "Ferroelectricity in Gd-doped HfO2 thin films," ECS J. Solid State Sci. 1, N123–N126 (2012).

- <sup>15</sup>T. Schenk, S. Mueller, U. Schroeder, R. Materlik, A. Kersch, M. Popovici, C. Adelmann, S. Van Elshocht, and T. Mikolajick, in 2013 Proceedings of the European Solid-State Device Research Conference (ESSDERC) (2013), pp. 260-263.

- <sup>16</sup>E. Yurchuk, J. Muller, S. Knebel, J. Sundqvist, A. P. Graham, T. Melde, U. Schroder, and T. Mikolajick, "Impact of layer thickness on the ferroelectric behaviour of silicon doped hafnium oxide thin films," Thin Solid Films 533, 88-92 (2013).

- <sup>17</sup>U. Schroeder, E. Yurchuk, J. Muller, D. Martin, T. Schenk, P. Polakowski, C. Adelmann, M. I. Popovici, S. V. Kalinin, and T. Mikolajick, "Impact of different dopants on the switching properties of ferroelectric hafniumoxide," Jpn. J. Appl. Phys. 53, 08LE02 (2014).

- <sup>18</sup>E. Yurchuk, J. Muller, J. Paul, T. Schlosser, D. Martin, R. Hoffmann, S. Muller, S. Slesazeck, U. Schroeder, R. Boschke, R. van Bentum, and T. Mikolajick, "Impact of scaling on the performance of HfO2-based ferroelectric field effect transistors," IEEE Trans. Electron Devices 61, 3699-3706 (2014).

- <sup>19</sup>T. Schenk, E. Yurchuk, S. Mueller, U. Schroeder, S. Starschich, U. Bottger, and T. Mikolajick, "About the deformation of ferroelectric hystereses," Appl. Phys. Rev. 1, 041103 (2014).

- <sup>20</sup>U. Schroeder, S. Mueller, J. Mueller, E. Yurchuk, D. Martin, C. Adelmann, T. Schloesser, R. van Bentum, and T. Mikolajick, "Hafnium oxide based CMOS compatible ferroelectric materials," ECS J. Solid State Sci. 2, N69-N72 (2013).

- <sup>21</sup>A. Chernikova, M. Kozodaev, A. Markeev, D. Negrov, M. Spiridonov, S. Zarubin, O. Bak, P. Buraohain, H. D. Lu, E. Suvorova, A. Gruverman, and A. Zenkevich, "Ultrathin Hf0.5Zr0.5O2 ferroelectric films on Si," ACS Appl. Mater. Interfaces 8, 7232–7237 (2016).

- <sup>22</sup>P. D. Lomenzo, Q. Takmeel, S. Moghaddam, and T. Nishida, "Annealing behavior of ferroelectric Si-doped HfO<sub>2</sub> thin films," Thin Solid Films 615, 139-144 (2016).

- <sup>23</sup>P. D. Lomenzo, Q. Takmeel, C. M. Fancher, C. Z. Zhou, N. G. Rudawski, S. Moghaddam, J. L. Jones, and T. Nishida, "Ferroelectric Si-doped HfO<sub>2</sub> device properties on highly doped germanium," IEEE Electron Device Lett. 36, 766–768 (2015).

- <sup>24</sup>P. D. Lomenzo, Q. Takmeel, C. Z. Zhou, Y. Liu, C. M. Fancher, J. L. Jones, S. Moghaddam, and T. Nishida, "The effects of layering in ferroelectric Si-doped HfO<sub>2</sub> thin films," Appl. Phys. Lett. 105, 072906 (2014).

- <sup>25</sup>N. Park, H. Kang, J. Park, Y. Lee, Y. Yun, J. H. Lee, S. G. Lee, Y. H. Lee, and D. Suh, "Ferroelectric single-crystal gated graphene/hexagonal-BN/ ferroelectric field-effect transistor," ACS Nano 9, 10729-10736 (2015).

- <sup>26</sup>A. Lipatov, P. Sharma, A. Gruverman, and A. Sinitskii, "Optoelectrical molybdenum disulfide (MoS2)-ferroelectric memories," ACS Nano 9, 8089-8098 (2015).

- <sup>27</sup>W. Lee, O. Kahya, C. T. Toh, B. Ozyilmaz, and J. H. Ahn, "Flexible graphene-PZT ferroelectric nonvolatile memory," Nanotechnology 24, 475202 (2013).

- <sup>28</sup>Y. Zheng, G. X. Ni, C. T. Toh, M. G. Zeng, S. T. Chen, K. Yao, and B. Ozyilmaz, "Gate-controlled nonvolatile graphene-ferroelectric memory," Appl. Phys. Lett. 94, 163505 (2009).

- <sup>29</sup>X. Hong, A. Posadas, K. Zou, CH. Ahn, and J. Zhu, "High-mobility fewlayer graphene field effect transistors fabricated on epitaxial ferroelectric gate oxides," Phys. Rev. Lett. 102, 136808 (2009).

- <sup>30</sup>C. Baeumer, S. P. Rogers, R. J. Xu, L. W. Martin, and M. Shim, "Tunable carrier type and density in graphene/PbZr0.2Ti0.8O3 hybrid structures through ferroelectric switching," Nano Lett. 13, 1693-1698 (2013).

- <sup>31</sup>J. F. Scott, C. A. Araujo, H. B. Meadows, L. D. Mcmillan, and A. Shawabkeh, "Radiation effects on ferroelectric thin-film memories-Retention failure mechanisms," J. Appl. Phys. 66, 1444-1453 (1989).

- <sup>32</sup>T. P. Ma, "Making silicon nitride film a viable gate dielectric," IEEE Trans. Electron Devices 45, 680–690 (1998).

- $^{33}\mbox{W. J. Zhu, T. Tamagawa, M. Gibson, T. Furukawa, and T. P. Ma, "Effect$ of Al inclusion in HfO2 on the physical and electrical properties of the dielectrics," IEEE Electron Device Lett. 23, 649-651 (2002).

- <sup>34</sup>S. M. Sze and K. K. Ng, *Physics of Semiconductor Devices*, 3rd ed. (Wiley-Interscience, 2007), p. 815.

- <sup>35</sup>T. Schenk, U. Schroeder, M. Pesic, M. Popovici, Y. V. Pershin, and T. Mikolajick, "Electric field cycling behavior of ferroelectric hafnium oxide," ACS Appl. Mater. Interfaces 6, 19744–19751 (2014).

- <sup>36</sup>E. Yurchuk, S. Mueller, D. Martin, S. Slesazeck, U. Schroeder, T. Mikolajick, J. Muller, J. Paul, R. Hoffmann, J. Sundqvist, T. Schlosser, R. Boschke, R. van Bentum, and M. Trentzsch, "Origin of the endurance degradation in the novel HfO2-based 1T ferroelectric non-volatile memories,' in International Reliability Physics Symposium (2014).